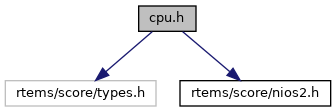

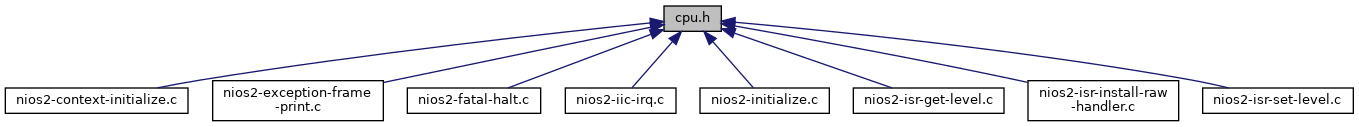

Altera Nios II CPU Department Source. More...

Go to the source code of this file.

Data Structures | |

| struct | Context_Control |

| This defines the minimal set of integer and processor state registers that must be saved during a voluntary context switch from one thread to another. More... | |

| struct | CPU_Exception_frame |

| The set of registers that specifies the complete processor state. More... | |

Macros | |

| #define | CPU_INLINE_ENABLE_DISPATCH FALSE |

| #define | CPU_HAS_SOFTWARE_INTERRUPT_STACK TRUE |

| #define | CPU_SIMPLE_VECTORED_INTERRUPTS TRUE |

| #define | CPU_INTERRUPT_NUMBER_OF_VECTORS 32 |

| #define | CPU_INTERRUPT_MAXIMUM_VECTOR_NUMBER (CPU_INTERRUPT_NUMBER_OF_VECTORS - 1) |

| #define | CPU_PROVIDES_ISR_IS_IN_PROGRESS TRUE |

| #define | CPU_HAS_HARDWARE_INTERRUPT_STACK FALSE |

| #define | CPU_ALLOCATE_INTERRUPT_STACK TRUE |

| #define | CPU_ISR_PASSES_FRAME_POINTER FALSE |

| #define | CPU_HARDWARE_FP FALSE |

| #define | CPU_SOFTWARE_FP FALSE |

| #define | CPU_CONTEXT_FP_SIZE 0 |

| #define | CPU_ALL_TASKS_ARE_FP FALSE |

| #define | CPU_IDLE_TASK_IS_FP FALSE |

| #define | CPU_USE_DEFERRED_FP_SWITCH FALSE |

| #define | CPU_PROVIDES_IDLE_THREAD_BODY FALSE |

| #define | CPU_STACK_GROWS_UP FALSE |

| #define | CPU_STRUCTURE_ALIGNMENT __attribute__((section(".sdata"), aligned(32))) |

| #define | CPU_TIMESTAMP_USE_INT64_INLINE TRUE |

| #define | CPU_BIG_ENDIAN FALSE |

| #define | CPU_LITTLE_ENDIAN TRUE |

| #define | CPU_STACK_MINIMUM_SIZE (4 * 1024) |

| #define | CPU_SIZEOF_POINTER 4 |

| #define | CPU_ALIGNMENT 4 |

| #define | CPU_HEAP_ALIGNMENT CPU_ALIGNMENT |

| #define | CPU_PARTITION_ALIGNMENT CPU_ALIGNMENT |

| #define | CPU_STACK_ALIGNMENT 4 |

| #define | CPU_MODES_INTERRUPT_MASK 0x3f |

| #define | CPU_USE_GENERIC_BITFIELD_CODE TRUE |

| #define | CPU_USE_GENERIC_BITFIELD_DATA TRUE |

| #define | CPU_MPCI_RECEIVE_SERVER_EXTRA_STACK 0 |

| #define | CPU_PER_CPU_CONTROL_SIZE 0 |

| #define | _CPU_Context_Get_SP(_context) (_context)->sp |

| #define | _CPU_Initialize_vectors() |

| #define | _CPU_ISR_Disable(_isr_cookie) |

| Macro to disable interrupts. More... | |

| #define | _CPU_ISR_Enable(_isr_cookie) __builtin_wrctl( 0, (int) _isr_cookie ) |

| Macro to restore the processor status. More... | |

| #define | _CPU_ISR_Flash(_isr_cookie) |

| Macro to restore the processor status and disable the interrupts again. More... | |

| #define | _CPU_Context_Restart_self(_the_context) _CPU_Context_restore( (_the_context) ); |

| #define | CPU_swap_u16(value) (((value&0xff) << 8) | ((value >> 8)&0xff)) |

Typedefs | |

| typedef void | CPU_Interrupt_frame |

| typedef uint32_t | CPU_Counter_ticks |

Functions | |

| void | _CPU_ISR_Set_level (uint32_t new_level) |

| Sets the interrupt level for the executing thread. More... | |

| uint32_t | _CPU_ISR_Get_level (void) |

| Returns the interrupt level of the executing thread. More... | |

| void | _CPU_Context_Initialize (Context_Control *context, void *stack_area_begin, size_t stack_area_size, uint32_t new_level, void(*entry_point)(void), bool is_fp, void *tls_area) |

| Initializes the CPU context. More... | |

| void | _CPU_Fatal_halt (uint32_t _source, uint32_t _error) |

| void | _CPU_Initialize (void) |

| CPU initialization. More... | |

| void | _CPU_ISR_install_raw_handler (uint32_t vector, proc_ptr new_handler, proc_ptr *old_handler) |

| CPU ISR install raw handler. More... | |

| void | _CPU_ISR_install_vector (uint32_t vector, proc_ptr new_handler, proc_ptr *old_handler) |

| CPU ISR install vector. More... | |

| void | _CPU_Context_switch (Context_Control *run, Context_Control *heir) |

| CPU switch context. More... | |

| void | _CPU_Context_restore (Context_Control *new_context) |

| This routine is generally used only to restart self in an efficient manner. More... | |

| void | _CPU_Context_volatile_clobber (uintptr_t pattern) |

| Clobbers all volatile registers with values derived from the pattern parameter. More... | |

| void | _CPU_Context_validate (uintptr_t pattern) |

| Initializes and validates the CPU context with values derived from the pattern parameter. More... | |

| void | _CPU_Exception_frame_print (const CPU_Exception_frame *frame) |

| Prints the exception frame via printk(). More... | |

| CPU_Counter_ticks | _CPU_Counter_read (void) |

Detailed Description

Altera Nios II CPU Department Source.

Macro Definition Documentation

◆ _CPU_ISR_Disable

| #define _CPU_ISR_Disable | ( | _isr_cookie | ) |

Macro to disable interrupts.

The processor status before disabling the interrupts will be stored in _isr_cookie. This value will be used in _CPU_ISR_Flash() and _CPU_ISR_Enable().

The global symbol _Nios2_ISR_Status_mask will be used to clear the bits in the status register representing the interrupt level. The global symbol _Nios2_ISR_Status_bits will be used to set the bits representing an interrupt level that disables interrupts. Both global symbols must be provided by the board support package.

In case the Nios II uses the internal interrupt controller (IIC), then only the PIE status bit is used.

In case the Nios II uses the external interrupt controller (EIC), then the RSIE status bit or the IL status field is used depending on the interrupt handling variant and the shadow register usage.

◆ _CPU_ISR_Enable

| #define _CPU_ISR_Enable | ( | _isr_cookie | ) | __builtin_wrctl( 0, (int) _isr_cookie ) |

Macro to restore the processor status.

The _isr_cookie must contain the processor status returned by _CPU_ISR_Disable(). The value is not modified.

◆ _CPU_ISR_Flash

| #define _CPU_ISR_Flash | ( | _isr_cookie | ) |

Macro to restore the processor status and disable the interrupts again.

The _isr_cookie must contain the processor status returned by _CPU_ISR_Disable(). The value is not modified.

This flash code is optimal for all Nios II configurations. The rdctl does not flush the pipeline and has only a late result penalty. The wrctl on the other hand leads to a pipeline flush.

1.8.13

1.8.13