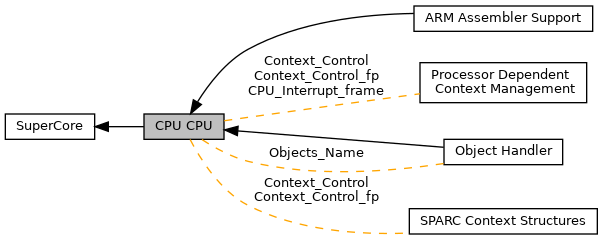

Provides CPU architecture dependent services. More...

|

Modules | |

| ARM Assembler Support | |

| ARM Assembler Support. | |

| Object Handler | |

Files | |

| file | arm_exc_handler_high.c |

| ARM exception support implementation. | |

| file | arm/cpu.c |

| ARM architecture support implementation. | |

| file | arm/rtems/score/cpu_asm.h |

| ARM Assembler Support API. | |

| file | epiphany-utility.h |

| This include file contains macros pertaining to the Epiphany processor family. | |

| file | objectshrinkinformation.c |

| Shrink an Object Class Information Record. | |

Data Structures | |

| struct | Context_Control |

| This defines the minimal set of integer and processor state registers that must be saved during a voluntary context switch from one thread to another. More... | |

| struct | Context_Control_fp |

| This defines the complete set of floating point registers that must be saved during any context switch from one thread to another. More... | |

| struct | CPU_Interrupt_frame |

| This defines the set of integer and processor state registers that must be saved during an interrupt. More... | |

| union | Objects_Name |

| The following type defines the control block used to manage object names. More... | |

Macros | |

| #define | CPU_MODEL_NAME "ARMv4" |

| #define | ARM_MULTILIB_ARCH_V4 |

| #define | CPU_NAME "ARM" |

| #define | CPU_INLINE_ENABLE_DISPATCH TRUE |

| #define | CPU_SIMPLE_VECTORED_INTERRUPTS FALSE |

| #define | CPU_HAS_SOFTWARE_INTERRUPT_STACK FALSE |

| #define | CPU_HAS_HARDWARE_INTERRUPT_STACK FALSE |

| #define | CPU_ALLOCATE_INTERRUPT_STACK FALSE |

| #define | CPU_ISR_PASSES_FRAME_POINTER 0 |

| #define | CPU_HARDWARE_FP FALSE |

| #define | CPU_SOFTWARE_FP FALSE |

| #define | CPU_ALL_TASKS_ARE_FP FALSE |

| #define | CPU_IDLE_TASK_IS_FP FALSE |

| #define | CPU_USE_DEFERRED_FP_SWITCH FALSE |

| #define | CPU_PROVIDES_IDLE_THREAD_BODY FALSE |

| #define | CPU_STACK_GROWS_UP FALSE |

| #define | CPU_STRUCTURE_ALIGNMENT __attribute__ ((aligned ( 32 ))) |

| #define | CPU_TIMESTAMP_USE_STRUCT_TIMESPEC TRUE |

| #define | CPU_MODES_INTERRUPT_MASK 0x1 |

| #define | CPU_CONTEXT_FP_SIZE sizeof( Context_Control_fp ) |

| #define | CPU_MPCI_RECEIVE_SERVER_EXTRA_STACK 0 |

| #define | CPU_PROVIDES_ISR_IS_IN_PROGRESS FALSE |

| #define | CPU_STACK_MINIMUM_SIZE (1024 * 4) |

| #define | CPU_SIZEOF_POINTER 4 |

| #define | CPU_ALIGNMENT 8 |

| #define | CPU_HEAP_ALIGNMENT CPU_ALIGNMENT |

| #define | CPU_PARTITION_ALIGNMENT 4 |

| #define | CPU_STACK_ALIGNMENT 8 |

| #define | CPU_USE_GENERIC_BITFIELD_CODE TRUE |

| #define | CPU_USE_GENERIC_BITFIELD_DATA TRUE |

| #define | CPU_PER_CPU_CONTROL_SIZE 0 |

| #define | _CPU_ISR_Disable(_isr_cookie) |

| #define | _CPU_ISR_Enable(_isr_cookie) arm_interrupt_enable( _isr_cookie ) |

| #define | _CPU_ISR_Flash(_isr_cookie) arm_interrupt_flash( _isr_cookie ) |

| #define | _CPU_Context_Get_SP(_context) (_context)->register_sp |

| #define | _CPU_Context_Restart_self(_the_context) _CPU_Context_restore( (_the_context) ); |

| #define | _CPU_Context_Fp_start(_base, _offset) ( (void *) _Addresses_Add_offset( (_base), (_offset) ) ) |

| #define | _CPU_Context_Initialize_fp(_destination) |

| #define | _CPU_Fatal_halt(_source, _err) |

| #define | CPU_INLINE_ENABLE_DISPATCH FALSE |

| #define | CPU_HAS_SOFTWARE_INTERRUPT_STACK FALSE |

| #define | CPU_SIMPLE_VECTORED_INTERRUPTS FALSE |

| #define | CPU_HAS_HARDWARE_INTERRUPT_STACK FALSE |

| #define | CPU_ALLOCATE_INTERRUPT_STACK FALSE |

| #define | CPU_ISR_PASSES_FRAME_POINTER 1 |

| #define | CPU_HARDWARE_FP FALSE |

| #define | CPU_ALL_TASKS_ARE_FP CPU_HARDWARE_FP |

| #define | CPU_IDLE_TASK_IS_FP FALSE |

| #define | CPU_USE_DEFERRED_FP_SWITCH TRUE |

| #define | CPU_PROVIDES_IDLE_THREAD_BODY TRUE |

| #define | CPU_STACK_GROWS_UP FALSE |

| #define | CPU_STRUCTURE_ALIGNMENT |

| #define | CPU_TIMESTAMP_USE_INT64_INLINE TRUE |

| #define | CPU_MODES_INTERRUPT_MASK 0x000000ff |

| #define | CPU_SIZEOF_POINTER 4 |

| #define | CPU_PER_CPU_CONTROL_SIZE 0 |

| #define | _CPU_Context_Get_SP(_context) (uintptr_t) (_context)->sp |

| #define | CPU_CONTEXT_FP_SIZE sizeof( Context_Control_fp ) |

| #define | CPU_MPCI_RECEIVE_SERVER_EXTRA_STACK 0 |

| #define | CPU_STACK_MINIMUM_SIZE (8 * 1024) |

| #define | CPU_ALIGNMENT 8 |

| #define | CPU_HEAP_ALIGNMENT CPU_ALIGNMENT |

| #define | CPU_PARTITION_ALIGNMENT CPU_ALIGNMENT |

| #define | CPU_STACK_ALIGNMENT CPU_ALIGNMENT |

| #define | _CPU_ISR_Disable(_level) |

| #define | _CPU_ISR_Enable(_level) |

| #define | _CPU_ISR_Flash(_xlevel) |

| #define | _CPU_Context_Restart_self(_the_context) _CPU_Context_restore( (_the_context) ); |

| #define | _CPU_Context_Fp_start(_base, _offset) ( (void *) _Addresses_Add_offset( (_base), (_offset) ) ) |

| #define | _CPU_Context_Initialize_fp(_destination) |

| #define | _CPU_Fatal_halt(_source, _error) |

| #define | CPU_USE_GENERIC_BITFIELD_CODE TRUE |

| #define | CPU_USE_GENERIC_BITFIELD_DATA TRUE |

| #define | _CPU_Bitfield_Find_first_bit(_value, _output) |

| #define | _CPU_Priority_Mask(_bit_number) ( 1 << (_bit_number) ) |

| #define | _CPU_Priority_bits_index(_priority) (_priority) |

| #define | CPU_swap_u16(value) (((value&0xff) << 8) | ((value >> 8)&0xff)) |

Typedefs | |

| typedef uint32_t | CPU_Counter_ticks |

| typedef uintptr_t | CPU_Uint32ptr |

| Type that can store a 32-bit integer or a pointer. More... | |

| typedef uint16_t | Priority_bit_map_Word |

| typedef uintptr_t | CPU_Uint32ptr |

| Type that can store a 32-bit integer or a pointer. More... | |

| typedef uint16_t | Priority_bit_map_Word |

| typedef void | epiphany_isr |

| typedef void(* | epiphany_isr_entry) (void) |

| typedef CPU_Interrupt_frame | CPU_Exception_frame |

| typedef uint32_t | CPU_Counter_ticks |

| typedef uintptr_t | CPU_Uint32ptr |

| Type that can store a 32-bit integer or a pointer. More... | |

| typedef uint16_t | Priority_bit_map_Word |

| typedef void | or1k_isr |

| typedef void(* | or1k_isr_entry) (void) |

Functions | |

| void | _CPU_ISR_Set_level (uint32_t level) |

| Sets the hardware interrupt level by the level value. More... | |

| void | _CPU_Context_Initialize (Context_Control *the_context, void *stack_area_begin, size_t stack_area_size, uint32_t new_level, void(*entry_point)(void), bool is_fp, void *tls_area) |

| void | _CPU_Initialize (void) |

| CPU initialization. More... | |

| CPU_Counter_ticks | _CPU_Counter_read (void) |

| CPU_Counter_ticks | _CPU_Counter_difference (CPU_Counter_ticks second, CPU_Counter_ticks first) |

| Returns the difference between the second and first CPU counter value. More... | |

| void * | _CPU_Thread_Idle_body (uintptr_t ignored) |

| void | mips_vector_exceptions (CPU_Interrupt_frame *frame) |

| uint32_t | mips_interrupt_mask (void) |

| void | _CPU_Context_Initialize (Context_Control *the_context, uintptr_t *stack_base, uint32_t size, uint32_t new_level, void *entry_point, bool is_fp, void *tls_area) |

| void | mips_break (int error) |

| void | _CPU_ISR_install_raw_handler (uint32_t vector, proc_ptr new_handler, proc_ptr *old_handler) |

| This routine installs a "raw" interrupt handler directly into the processor's vector table. More... | |

| void | _CPU_Install_interrupt_stack (void) |

| This routine installs the hardware interrupt stack pointer. More... | |

| void | _CPU_Context_save_fp (Context_Control_fp **fp_context_ptr) |

| This routine saves the floating point context passed to it. More... | |

| void | _CPU_Context_restore_fp (Context_Control_fp **fp_context_ptr) |

| This routine restores the floating point context passed to it. More... | |

| void | _CPU_Exception_frame_print (const CPU_Exception_frame *frame) |

| Prints the exception frame via printk(). More... | |

Variables | |

| uint32_t | arm_cpu_mode |

| SCORE_EXTERN Context_Control_fp | _CPU_Null_fp_context |

Detailed Description

Provides CPU architecture dependent services.

Macro Definition Documentation

◆ _CPU_Bitfield_Find_first_bit

| #define _CPU_Bitfield_Find_first_bit | ( | _value, | |

| _output | |||

| ) |

◆ _CPU_Context_Initialize_fp [1/2]

| #define _CPU_Context_Initialize_fp | ( | _destination | ) |

◆ _CPU_Context_Initialize_fp [2/2]

| #define _CPU_Context_Initialize_fp | ( | _destination | ) |

◆ _CPU_Fatal_halt [1/2]

| #define _CPU_Fatal_halt | ( | _source, | |

| _err | |||

| ) |

◆ _CPU_Fatal_halt [2/2]

| #define _CPU_Fatal_halt | ( | _source, | |

| _error | |||

| ) |

◆ _CPU_ISR_Disable [1/2]

| #define _CPU_ISR_Disable | ( | _isr_cookie | ) |

◆ _CPU_ISR_Disable [2/2]

| #define _CPU_ISR_Disable | ( | _level | ) |

◆ _CPU_ISR_Enable

| #define _CPU_ISR_Enable | ( | _level | ) |

◆ _CPU_ISR_Flash

| #define _CPU_ISR_Flash | ( | _xlevel | ) |

Typedef Documentation

◆ CPU_Uint32ptr [1/3]

| typedef uintptr_t CPU_Uint32ptr |

Type that can store a 32-bit integer or a pointer.

◆ CPU_Uint32ptr [2/3]

| typedef uintptr_t CPU_Uint32ptr |

Type that can store a 32-bit integer or a pointer.

◆ CPU_Uint32ptr [3/3]

| typedef uintptr_t CPU_Uint32ptr |

Type that can store a 32-bit integer or a pointer.

Function Documentation

◆ _CPU_Context_restore_fp()

| void _CPU_Context_restore_fp | ( | Context_Control_fp ** | fp_context_ptr | ) |

This routine restores the floating point context passed to it.

- Parameters

-

[in] fp_context_ptr is a pointer to a pointer to a floating point context area to restore

- Returns

- on output *fp_context_ptr will contain the address that should be used with _CPU_Context_save_fp to save this context.

Port Specific Information:

XXX document implementation including references if appropriate

◆ _CPU_Context_save_fp()

| void _CPU_Context_save_fp | ( | Context_Control_fp ** | fp_context_ptr | ) |

This routine saves the floating point context passed to it.

- Parameters

-

[in] fp_context_ptr is a pointer to a pointer to a floating point context area

- Returns

- on output *fp_context_ptr will contain the address that should be used with _CPU_Context_restore_fp to restore this context.

Port Specific Information:

XXX document implementation including references if appropriate

◆ _CPU_Counter_difference()

|

inline |

Returns the difference between the second and first CPU counter value.

This operation may be carried out as a modulo operation depending on the range of the CPU counter device.

- Parameters

-

[in] second The second CPU counter value. [in] first The first CPU counter value.

- Returns

- Returns second minus first modulo counter period.

◆ _CPU_Exception_frame_print()

| void _CPU_Exception_frame_print | ( | const CPU_Exception_frame * | frame | ) |

Prints the exception frame via printk().

This method prints the CPU exception frame.

- See also

- rtems_fatal() and RTEMS_FATAL_SOURCE_EXCEPTION.

Referenced by _CPU_Context_validate().

◆ _CPU_Initialize()

| void _CPU_Initialize | ( | void | ) |

CPU initialization.

CPU initialization.

◆ _CPU_Install_interrupt_stack()

| void _CPU_Install_interrupt_stack | ( | void | ) |

This routine installs the hardware interrupt stack pointer.

NOTE: It need only be provided if CPU_HAS_HARDWARE_INTERRUPT_STACK is TRUE.

Port Specific Information:

XXX document implementation including references if appropriate

◆ _CPU_ISR_install_raw_handler()

This routine installs a "raw" interrupt handler directly into the processor's vector table.

- Parameters

-

[in] vector is the vector number [in] new_handler is the raw ISR handler to install [in] old_handler is the previously installed ISR Handler

Port Specific Information:

XXX document implementation including references if appropriate

◆ _CPU_ISR_Set_level()

| void _CPU_ISR_Set_level | ( | uint32_t | level | ) |

Sets the hardware interrupt level by the level value.

- Parameters

-

[in] level for or1k can only range over two values: 0 (enable interrupts) and 1 (disable interrupts). In future implementations if fast context switch is implemented, the level can range from 0 to 15.

- See also

- OpenRISC architecture manual.

1.8.13

1.8.13