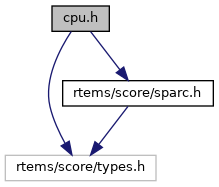

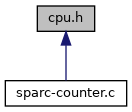

SPARC CPU Department Source. More...

Go to the source code of this file.

Data Structures | |

| struct | CPU_Minimum_stack_frame |

| This structure represents the organization of the minimum stack frame for the SPARC. More... | |

| struct | CPU_Per_CPU_control |

| The CPU specific per-CPU control. More... | |

| struct | Context_Control |

| This defines the minimal set of integer and processor state registers that must be saved during a voluntary context switch from one thread to another. More... | |

| struct | Context_Control_fp |

| This defines the complete set of floating point registers that must be saved during any context switch from one thread to another. More... | |

| struct | CPU_Interrupt_frame |

| This defines the set of integer and processor state registers that must be saved during an interrupt. More... | |

| struct | CPU_Trap_table_entry |

| The following type defines an entry in the SPARC's trap table. More... | |

| struct | CPU_Exception_frame |

| The set of registers that specifies the complete processor state. More... | |

| struct | SPARC_Counter |

Macros | |

| #define | CPU_INLINE_ENABLE_DISPATCH TRUE |

| Should the calls to _Thread_Enable_dispatch be inlined? More... | |

| #define | CPU_HAS_SOFTWARE_INTERRUPT_STACK TRUE |

| Does the executive manage a dedicated interrupt stack in software? More... | |

| #define | CPU_SIMPLE_VECTORED_INTERRUPTS TRUE |

| Does the CPU follow the simple vectored interrupt model? More... | |

| #define | CPU_HAS_HARDWARE_INTERRUPT_STACK FALSE |

| Does this CPU have hardware support for a dedicated interrupt stack? More... | |

| #define | CPU_ALLOCATE_INTERRUPT_STACK TRUE |

| Do we allocate a dedicated interrupt stack in the Interrupt Manager? More... | |

| #define | CPU_ISR_PASSES_FRAME_POINTER 0 |

| Does the RTEMS invoke the user's ISR with the vector number and a pointer to the saved interrupt frame (1) or just the vector number (0)? More... | |

| #define | CPU_HARDWARE_FP FALSE |

| Does the CPU have hardware floating point? More... | |

| #define | CPU_SOFTWARE_FP FALSE |

| The SPARC GCC port does not have a software floating point library that requires RTEMS assistance. | |

| #define | CPU_ALL_TASKS_ARE_FP FALSE |

| Are all tasks FLOATING_POINT tasks implicitly? More... | |

| #define | CPU_IDLE_TASK_IS_FP FALSE |

| Should the IDLE task have a floating point context? More... | |

| #define | CPU_USE_DEFERRED_FP_SWITCH TRUE |

| Should the saving of the floating point registers be deferred until a context switch is made to another different floating point task? More... | |

| #define | CPU_PROVIDES_IDLE_THREAD_BODY FALSE |

| Does this port provide a CPU dependent IDLE task implementation? More... | |

| #define | CPU_STACK_GROWS_UP FALSE |

| Does the stack grow up (toward higher addresses) or down (toward lower addresses)? More... | |

| #define | CPU_STRUCTURE_ALIGNMENT __attribute__ ((aligned (32))) |

| The following is the variable attribute used to force alignment of critical data structures. More... | |

| #define | CPU_TIMESTAMP_USE_INT64_INLINE TRUE |

| #define | CPU_BIG_ENDIAN TRUE |

| Define what is required to specify how the network to host conversion routines are handled. More... | |

| #define | CPU_LITTLE_ENDIAN FALSE |

| Define what is required to specify how the network to host conversion routines are handled. More... | |

| #define | CPU_MODES_INTERRUPT_MASK 0x0000000F |

| The following defines the number of bits actually used in the interrupt field of the task mode. More... | |

| #define | CPU_STACK_FRAME_L0_OFFSET 0x00 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_L1_OFFSET 0x04 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_L2_OFFSET 0x08 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_L3_OFFSET 0x0c |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_L4_OFFSET 0x10 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_L5_OFFSET 0x14 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_L6_OFFSET 0x18 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_L7_OFFSET 0x1c |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_I0_OFFSET 0x20 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_I1_OFFSET 0x24 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_I2_OFFSET 0x28 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_I3_OFFSET 0x2c |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_I4_OFFSET 0x30 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_I5_OFFSET 0x34 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_I6_FP_OFFSET 0x38 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_I7_OFFSET 0x3c |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STRUCTURE_RETURN_ADDRESS_OFFSET 0x40 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_SAVED_ARG0_OFFSET 0x44 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_SAVED_ARG1_OFFSET 0x48 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_SAVED_ARG2_OFFSET 0x4c |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_SAVED_ARG3_OFFSET 0x50 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_SAVED_ARG4_OFFSET 0x54 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_SAVED_ARG5_OFFSET 0x58 |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_STACK_FRAME_PAD0_OFFSET 0x5c |

| This macro defines an offset into the stack frame for use in assembly. More... | |

| #define | CPU_MINIMUM_STACK_FRAME_SIZE 0x60 |

| This defines the size of the minimum stack frame. More... | |

| #define | CPU_PER_CPU_CONTROL_SIZE 4 |

| #define | SPARC_PER_CPU_ISR_DISPATCH_DISABLE 0 |

| Offset of the CPU_Per_CPU_control::isr_dispatch_disable field relative to the Per_CPU_Control begin. | |

| #define | _CPU_Context_Get_SP(_context) (_context)->o6_sp |

| This macro provides a CPU independent way for RTEMS to access the stack pointer in a context structure. More... | |

| #define | G5_OFFSET 0x00 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | G7_OFFSET 0x04 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | L0_OFFSET 0x08 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | L1_OFFSET 0x0C |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | L2_OFFSET 0x10 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | L3_OFFSET 0x14 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | L4_OFFSET 0x18 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | L5_OFFSET 0x1C |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | L6_OFFSET 0x20 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | L7_OFFSET 0x24 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | I0_OFFSET 0x28 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | I1_OFFSET 0x2C |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | I2_OFFSET 0x30 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | I3_OFFSET 0x34 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | I4_OFFSET 0x38 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | I5_OFFSET 0x3C |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | I6_FP_OFFSET 0x40 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | I7_OFFSET 0x44 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | O6_SP_OFFSET 0x48 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | O7_OFFSET 0x4C |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | PSR_OFFSET 0x50 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | ISR_DISPATCH_DISABLE_STACK_OFFSET 0x54 |

| This macro defines an offset into the context for use in assembly. More... | |

| #define | FO_F1_OFFSET 0x00 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F2_F3_OFFSET 0x08 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F4_F5_OFFSET 0x10 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F6_F7_OFFSET 0x18 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F8_F9_OFFSET 0x20 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F1O_F11_OFFSET 0x28 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F12_F13_OFFSET 0x30 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F14_F15_OFFSET 0x38 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F16_F17_OFFSET 0x40 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F18_F19_OFFSET 0x48 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F2O_F21_OFFSET 0x50 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F22_F23_OFFSET 0x58 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F24_F25_OFFSET 0x60 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F26_F27_OFFSET 0x68 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F28_F29_OFFSET 0x70 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | F3O_F31_OFFSET 0x78 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | FSR_OFFSET 0x80 |

| This macro defines an offset into the FPU context for use in assembly. More... | |

| #define | CONTEXT_CONTROL_FP_SIZE 0x84 |

| This defines the size of the FPU context area for use in assembly. More... | |

| #define | ISF_PSR_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x00 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_PC_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x04 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_NPC_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x08 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_G1_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x0c |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_G2_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x10 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_G3_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x14 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_G4_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x18 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_G5_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x1c |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_G7_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x24 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_I0_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x28 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_I1_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x2c |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_I2_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x30 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_I3_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x34 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_I4_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x38 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_I5_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x3c |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_I6_FP_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x40 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_I7_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x44 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_Y_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x48 |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | ISF_TPC_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x4c |

| This macro defines an offset into the ISF for use in assembly. More... | |

| #define | CONTEXT_CONTROL_INTERRUPT_FRAME_SIZE CPU_MINIMUM_STACK_FRAME_SIZE + 0x50 |

| This defines the size of the ISF area for use in assembly. More... | |

| #define | CPU_CONTEXT_FP_SIZE sizeof( Context_Control_fp ) |

| The size of the floating point context area. | |

| #define | CPU_MPCI_RECEIVE_SERVER_EXTRA_STACK 1024 |

| Amount of extra stack (above minimum stack size) required by MPCI receive server thread. More... | |

| #define | CPU_INTERRUPT_NUMBER_OF_VECTORS 256 |

| This defines the number of entries in the ISR_Vector_table managed by the executive. More... | |

| #define | CPU_INTERRUPT_MAXIMUM_VECTOR_NUMBER 511 |

| The SPARC has 256 vectors but the port treats 256-512 as synchronous traps. | |

| #define | SPARC_SYNCHRONOUS_TRAP_BIT_MASK 0x100 |

| This is the bit step in a vector number to indicate it is being installed as a synchronous trap. | |

| #define | SPARC_ASYNCHRONOUS_TRAP(_trap) (_trap) |

| This macro indicates that _trap as an asynchronous trap. | |

| #define | SPARC_SYNCHRONOUS_TRAP(_trap) ((_trap) + 256 ) |

| This macro indicates that _trap as a synchronous trap. | |

| #define | SPARC_REAL_TRAP_NUMBER(_trap) ((_trap) % 256) |

| This macro returns the real hardware vector number associated with _trap. | |

| #define | CPU_PROVIDES_ISR_IS_IN_PROGRESS FALSE |

| This is defined if the port has a special way to report the ISR nesting level. More... | |

| #define | CPU_STACK_MINIMUM_SIZE (1024*4) |

| Should be large enough to run all tests. More... | |

| #define | CPU_SIZEOF_POINTER 4 |

| What is the size of a pointer on this architecture? | |

| #define | CPU_ALIGNMENT 8 |

| CPU's worst alignment requirement for data types on a byte boundary. More... | |

| #define | CPU_HEAP_ALIGNMENT CPU_ALIGNMENT |

| This number corresponds to the byte alignment requirement for the heap handler. More... | |

| #define | CPU_PARTITION_ALIGNMENT CPU_ALIGNMENT |

| This number corresponds to the byte alignment requirement for memory buffers allocated by the partition manager. More... | |

| #define | CPU_STACK_ALIGNMENT 16 |

| This number corresponds to the byte alignment requirement for the stack. More... | |

| #define | _CPU_Initialize_vectors() |

| Support routine to initialize the RTEMS vector table after it is allocated. | |

| #define | _CPU_ISR_Disable(_level) (_level) = sparc_disable_interrupts() |

| Disable all interrupts for a critical section. More... | |

| #define | _CPU_ISR_Enable(_level) sparc_enable_interrupts( _level ) |

| Enable interrupts to the previous level (returned by _CPU_ISR_Disable). More... | |

| #define | _CPU_ISR_Flash(_level) sparc_flash_interrupts( _level ) |

| This temporarily restores the interrupt to _level before immediately disabling them again. More... | |

| #define | _CPU_ISR_Set_level(_newlevel) sparc_enable_interrupts( _newlevel << 8) |

| Map interrupt level in task mode onto the hardware that the CPU actually provides. More... | |

| #define | _CPU_Context_Initialization_at_thread_begin() |

| This macro is invoked from _Thread_Handler to do whatever CPU specific magic is required that must be done in the context of the thread when it starts. More... | |

| #define | _CPU_Context_Restart_self(_the_context) _CPU_Context_restore( (_the_context) ); |

| This routine is responsible for somehow restarting the currently executing task. More... | |

| #define | _CPU_Context_Fp_start(_base, _offset) ( (void *) _Addresses_Add_offset( (_base), (_offset) ) ) |

| The FP context area for the SPARC is a simple structure and nothing special is required to find the "starting load point". | |

| #define | _CPU_Context_Initialize_fp(_destination) |

| This routine initializes the FP context area passed to it to. More... | |

| #define | CPU_USE_GENERIC_BITFIELD_CODE TRUE |

| The SPARC port uses the generic C algorithm for bitfield scan if the CPU model does not have a scan instruction. | |

| #define | CPU_USE_GENERIC_BITFIELD_DATA TRUE |

| The SPARC port uses the generic C algorithm for bitfield scan if the CPU model does not have a scan instruction. More... | |

| #define | _CPU_Get_current_per_CPU_control() ( _SPARC_Per_CPU_current ) |

| #define | CPU_swap_u16(value) (((value&0xff) << 8) | ((value >> 8)&0xff)) |

| SPARC specific method to endian swap an uint16_t. More... | |

Typedefs | |

| typedef uint32_t | CPU_Counter_ticks |

| typedef CPU_Counter_ticks(* | SPARC_Counter_difference) (CPU_Counter_ticks second, CPU_Counter_ticks first) |

Functions | |

| uint32_t | _CPU_ISR_Get_level (void) |

| Obtain the current interrupt disable level. More... | |

| void | _CPU_Context_Initialize (Context_Control *the_context, uint32_t *stack_base, uint32_t size, uint32_t new_level, void *entry_point, bool is_fp, void *tls_area) |

| Initialize the context to a state suitable for starting a task after a context restore operation. More... | |

| void | _CPU_Fatal_halt (uint32_t source, uint32_t error) |

| This routine copies _error into a known place – typically a stack location or a register, optionally disables interrupts, and halts/stops the CPU. | |

| void | _CPU_Initialize (void) |

| SPARC specific initialization. More... | |

| void | _CPU_ISR_install_raw_handler (uint32_t vector, proc_ptr new_handler, proc_ptr *old_handler) |

| SPARC specific raw ISR installer. More... | |

| void | _CPU_ISR_install_vector (uint32_t vector, proc_ptr new_handler, proc_ptr *old_handler) |

| SPARC specific RTEMS ISR installer. More... | |

| void | _CPU_Context_switch (Context_Control *run, Context_Control *heir) |

| SPARC specific context switch. More... | |

| void | _CPU_Context_restore (Context_Control *new_context) |

| SPARC specific context restore. More... | |

| register struct Per_CPU_Control *_SPARC_Per_CPU_current | __asm__ ("g6") |

| The pointer to the current per-CPU control is available via register g6. | |

| void | _CPU_Context_save_fp (Context_Control_fp **fp_context_ptr) |

| SPARC specific save FPU method. More... | |

| void | _CPU_Context_restore_fp (Context_Control_fp **fp_context_ptr) |

| SPARC specific restore FPU method. More... | |

| void | _CPU_Context_volatile_clobber (uintptr_t pattern) |

| Clobbers all volatile registers with values derived from the pattern parameter. More... | |

| void | _CPU_Context_validate (uintptr_t pattern) |

| Initializes and validates the CPU context with values derived from the pattern parameter. More... | |

| void | _CPU_Exception_frame_print (const CPU_Exception_frame *frame) |

| Prints the exception frame via printk(). More... | |

| CPU_Counter_ticks | _SPARC_Counter_difference_default (CPU_Counter_ticks second, CPU_Counter_ticks first) |

Variables | |

| SCORE_EXTERN Context_Control_fp _CPU_Null_fp_context | CPU_STRUCTURE_ALIGNMENT |

| This variable is contains the initialize context for the FP unit. More... | |

| const CPU_Trap_table_entry | _CPU_Trap_slot_template |

| This is the set of opcodes for the instructions loaded into a trap table entry. More... | |

| SPARC_Counter | _SPARC_Counter |

Detailed Description

SPARC CPU Department Source.

This include file contains information pertaining to the port of the executive to the SPARC processor.

Macro Definition Documentation

◆ _CPU_Context_Initialization_at_thread_begin

| #define _CPU_Context_Initialization_at_thread_begin | ( | ) |

This macro is invoked from _Thread_Handler to do whatever CPU specific magic is required that must be done in the context of the thread when it starts.

On the SPARC, this is setting the frame pointer so GDB is happy. Make GDB stop unwinding at _Thread_Handler, previous register window Frame pointer is 0 and calling address must be a function with starting with a SAVE instruction. If return address is leaf-function (no SAVE) GDB will not look at prev reg window fp.

_Thread_Handler is known to start with SAVE.

◆ _CPU_Context_Initialize_fp

| #define _CPU_Context_Initialize_fp | ( | _destination | ) |

This routine initializes the FP context area passed to it to.

The SPARC allows us to use the simple initialization model in which an "initial" FP context was saved into _CPU_Null_fp_context at CPU initialization and it is simply copied into the destination context.

◆ _CPU_Context_Restart_self

| #define _CPU_Context_Restart_self | ( | _the_context | ) | _CPU_Context_restore( (_the_context) ); |

This routine is responsible for somehow restarting the currently executing task.

On the SPARC, this is is relatively painless but requires a small amount of wrapper code before using the regular restore code in of the context switch.

◆ _CPU_ISR_Disable

| #define _CPU_ISR_Disable | ( | _level | ) | (_level) = sparc_disable_interrupts() |

Disable all interrupts for a critical section.

The previous level is returned in _level.

◆ _CPU_ISR_Enable

| #define _CPU_ISR_Enable | ( | _level | ) | sparc_enable_interrupts( _level ) |

Enable interrupts to the previous level (returned by _CPU_ISR_Disable).

This indicates the end of a critical section. The parameter _level is not modified.

◆ _CPU_ISR_Flash

| #define _CPU_ISR_Flash | ( | _level | ) | sparc_flash_interrupts( _level ) |

This temporarily restores the interrupt to _level before immediately disabling them again.

This is used to divide long critical sections into two or more parts. The parameter _level is not modified.

◆ _CPU_ISR_Set_level

| #define _CPU_ISR_Set_level | ( | _newlevel | ) | sparc_enable_interrupts( _newlevel << 8) |

Map interrupt level in task mode onto the hardware that the CPU actually provides.

Currently, interrupt levels which do not map onto the CPU in a straight fashion are undefined.

◆ CONTEXT_CONTROL_INTERRUPT_FRAME_SIZE

| #define CONTEXT_CONTROL_INTERRUPT_FRAME_SIZE CPU_MINIMUM_STACK_FRAME_SIZE + 0x50 |

This defines the size of the ISF area for use in assembly.

◆ CPU_ALIGNMENT

| #define CPU_ALIGNMENT 8 |

CPU's worst alignment requirement for data types on a byte boundary.

This alignment does not take into account the requirements for the stack.

On the SPARC, this is required for double word loads and stores.

◆ CPU_ALL_TASKS_ARE_FP

| #define CPU_ALL_TASKS_ARE_FP FALSE |

Are all tasks FLOATING_POINT tasks implicitly?

- If TRUE, then the FLOATING_POINT task attribute is assumed.

- If FALSE, then the FLOATING_POINT task attribute is followed.

The SPARC GCC port does not implicitly use floating point registers.

◆ CPU_ALLOCATE_INTERRUPT_STACK

| #define CPU_ALLOCATE_INTERRUPT_STACK TRUE |

Do we allocate a dedicated interrupt stack in the Interrupt Manager?

- If TRUE, then the memory is allocated during initialization.

- If FALSE, then the memory is allocated during initialization.

The SPARC does not have hardware support for switching to a dedicated interrupt stack. The port includes support for doing this in software.

◆ CPU_BIG_ENDIAN

| #define CPU_BIG_ENDIAN TRUE |

Define what is required to specify how the network to host conversion routines are handled.

The SPARC is big endian.

◆ CPU_HARDWARE_FP

| #define CPU_HARDWARE_FP FALSE |

Does the CPU have hardware floating point?

- If TRUE, then the FLOATING_POINT task attribute is supported.

- If FALSE, then the FLOATING_POINT task attribute is ignored.

This is set based upon the multilib settings.

◆ CPU_HAS_HARDWARE_INTERRUPT_STACK

| #define CPU_HAS_HARDWARE_INTERRUPT_STACK FALSE |

Does this CPU have hardware support for a dedicated interrupt stack?

- If TRUE, then it must be installed during initialization.

- If FALSE, then no installation is performed.

The SPARC does not have a dedicated HW interrupt stack.

◆ CPU_HAS_SOFTWARE_INTERRUPT_STACK

| #define CPU_HAS_SOFTWARE_INTERRUPT_STACK TRUE |

Does the executive manage a dedicated interrupt stack in software?

If TRUE, then a stack is allocated in _ISR_Handler_initialization. If FALSE, nothing is done.

The SPARC does not have a dedicated HW interrupt stack and one has been implemented in SW.

◆ CPU_HEAP_ALIGNMENT

| #define CPU_HEAP_ALIGNMENT CPU_ALIGNMENT |

This number corresponds to the byte alignment requirement for the heap handler.

This alignment requirement may be stricter than that for the data types alignment specified by CPU_ALIGNMENT. It is common for the heap to follow the same alignment requirement as CPU_ALIGNMENT. If the CPU_ALIGNMENT is strict enough for the heap, then this should be set to CPU_ALIGNMENT.

NOTE: This does not have to be a power of 2. It does have to be greater or equal to than CPU_ALIGNMENT.

◆ CPU_IDLE_TASK_IS_FP

| #define CPU_IDLE_TASK_IS_FP FALSE |

Should the IDLE task have a floating point context?

- If TRUE, then the IDLE task is created as a FLOATING_POINT task and it has a floating point context which is switched in and out.

- If FALSE, then the IDLE task does not have a floating point context.

The IDLE task does not have to be floating point on the SPARC.

◆ CPU_INLINE_ENABLE_DISPATCH

| #define CPU_INLINE_ENABLE_DISPATCH TRUE |

Should the calls to _Thread_Enable_dispatch be inlined?

- If TRUE, then they are inlined.

- If FALSE, then a subroutine call is made.

On this port, it is faster to inline _Thread_Enable_dispatch.

◆ CPU_INTERRUPT_NUMBER_OF_VECTORS

| #define CPU_INTERRUPT_NUMBER_OF_VECTORS 256 |

This defines the number of entries in the ISR_Vector_table managed by the executive.

On the SPARC, there are really only 256 vectors. However, the executive has no easy, fast, reliable way to determine which traps are synchronous and which are asynchronous. By default, synchronous traps return to the instruction which caused the interrupt. So if you install a software trap handler as an executive interrupt handler (which is desirable since RTEMS takes care of window and register issues), then the executive needs to know that the return address is to the trap rather than the instruction following the trap.

So vectors 0 through 255 are treated as regular asynchronous traps which provide the "correct" return address. Vectors 256 through 512 are assumed by the executive to be synchronous and to require that the return address be fudged.

If you use this mechanism to install a trap handler which must reexecute the instruction which caused the trap, then it should be installed as an asynchronous trap. This will avoid the executive changing the return address.

◆ CPU_ISR_PASSES_FRAME_POINTER

| #define CPU_ISR_PASSES_FRAME_POINTER 0 |

Does the RTEMS invoke the user's ISR with the vector number and a pointer to the saved interrupt frame (1) or just the vector number (0)?

The SPARC port does not pass an Interrupt Stack Frame pointer to interrupt handlers.

◆ CPU_LITTLE_ENDIAN

| #define CPU_LITTLE_ENDIAN FALSE |

Define what is required to specify how the network to host conversion routines are handled.

The SPARC is NOT little endian.

◆ CPU_MINIMUM_STACK_FRAME_SIZE

| #define CPU_MINIMUM_STACK_FRAME_SIZE 0x60 |

This defines the size of the minimum stack frame.

◆ CPU_MODES_INTERRUPT_MASK

| #define CPU_MODES_INTERRUPT_MASK 0x0000000F |

The following defines the number of bits actually used in the interrupt field of the task mode.

How those bits map to the CPU interrupt levels is defined by the routine _CPU_ISR_Set_level().

The SPARC has 16 interrupt levels in the PIL field of the PSR.

◆ CPU_MPCI_RECEIVE_SERVER_EXTRA_STACK

| #define CPU_MPCI_RECEIVE_SERVER_EXTRA_STACK 1024 |

Amount of extra stack (above minimum stack size) required by MPCI receive server thread.

Remember that in a multiprocessor system this thread must exist and be able to process all directives.

◆ CPU_PARTITION_ALIGNMENT

| #define CPU_PARTITION_ALIGNMENT CPU_ALIGNMENT |

This number corresponds to the byte alignment requirement for memory buffers allocated by the partition manager.

This alignment requirement may be stricter than that for the data types alignment specified by CPU_ALIGNMENT. It is common for the partition to follow the same alignment requirement as CPU_ALIGNMENT. If the CPU_ALIGNMENT is strict enough for the partition, then this should be set to CPU_ALIGNMENT.

NOTE: This does not have to be a power of 2. It does have to be greater or equal to than CPU_ALIGNMENT.

◆ CPU_PROVIDES_IDLE_THREAD_BODY

| #define CPU_PROVIDES_IDLE_THREAD_BODY FALSE |

Does this port provide a CPU dependent IDLE task implementation?

- If TRUE, then the routine _CPU_Thread_Idle_body must be provided and is the default IDLE thread body instead of _CPU_Thread_Idle_body.

- If FALSE, then use the generic IDLE thread body if the BSP does not provide one.

The SPARC architecture does not have a low power or halt instruction. It is left to the BSP and/or CPU specific code to provide an IDLE thread body which is aware of low power modes.

◆ CPU_PROVIDES_ISR_IS_IN_PROGRESS

| #define CPU_PROVIDES_ISR_IS_IN_PROGRESS FALSE |

This is defined if the port has a special way to report the ISR nesting level.

Most ports maintain the variable _ISR_Nest_level.

◆ CPU_SIMPLE_VECTORED_INTERRUPTS

| #define CPU_SIMPLE_VECTORED_INTERRUPTS TRUE |

Does the CPU follow the simple vectored interrupt model?

- If TRUE, then RTEMS allocates the vector table it internally manages.

- If FALSE, then the BSP is assumed to allocate and manage the vector table

THe SPARC is a simple vectored architecture. Usually there is no PIC and the CPU directly vectors the interrupts.

◆ CPU_STACK_ALIGNMENT

| #define CPU_STACK_ALIGNMENT 16 |

This number corresponds to the byte alignment requirement for the stack.

This alignment requirement may be stricter than that for the data types alignment specified by CPU_ALIGNMENT. If the CPU_ALIGNMENT is strict enough for the stack, then this should be set to 0.

NOTE: This must be a power of 2 either 0 or greater than CPU_ALIGNMENT.

The alignment restrictions for the SPARC are not that strict but this should unsure that the stack is always sufficiently alignment that the window overflow, underflow, and flush routines can use double word loads and stores.

◆ CPU_STACK_FRAME_I0_OFFSET

| #define CPU_STACK_FRAME_I0_OFFSET 0x20 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_I1_OFFSET

| #define CPU_STACK_FRAME_I1_OFFSET 0x24 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_I2_OFFSET

| #define CPU_STACK_FRAME_I2_OFFSET 0x28 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_I3_OFFSET

| #define CPU_STACK_FRAME_I3_OFFSET 0x2c |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_I4_OFFSET

| #define CPU_STACK_FRAME_I4_OFFSET 0x30 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_I5_OFFSET

| #define CPU_STACK_FRAME_I5_OFFSET 0x34 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_I6_FP_OFFSET

| #define CPU_STACK_FRAME_I6_FP_OFFSET 0x38 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_I7_OFFSET

| #define CPU_STACK_FRAME_I7_OFFSET 0x3c |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_L0_OFFSET

| #define CPU_STACK_FRAME_L0_OFFSET 0x00 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_L1_OFFSET

| #define CPU_STACK_FRAME_L1_OFFSET 0x04 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_L2_OFFSET

| #define CPU_STACK_FRAME_L2_OFFSET 0x08 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_L3_OFFSET

| #define CPU_STACK_FRAME_L3_OFFSET 0x0c |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_L4_OFFSET

| #define CPU_STACK_FRAME_L4_OFFSET 0x10 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_L5_OFFSET

| #define CPU_STACK_FRAME_L5_OFFSET 0x14 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_L6_OFFSET

| #define CPU_STACK_FRAME_L6_OFFSET 0x18 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_L7_OFFSET

| #define CPU_STACK_FRAME_L7_OFFSET 0x1c |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_PAD0_OFFSET

| #define CPU_STACK_FRAME_PAD0_OFFSET 0x5c |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_SAVED_ARG0_OFFSET

| #define CPU_STACK_FRAME_SAVED_ARG0_OFFSET 0x44 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_SAVED_ARG1_OFFSET

| #define CPU_STACK_FRAME_SAVED_ARG1_OFFSET 0x48 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_SAVED_ARG2_OFFSET

| #define CPU_STACK_FRAME_SAVED_ARG2_OFFSET 0x4c |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_SAVED_ARG3_OFFSET

| #define CPU_STACK_FRAME_SAVED_ARG3_OFFSET 0x50 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_SAVED_ARG4_OFFSET

| #define CPU_STACK_FRAME_SAVED_ARG4_OFFSET 0x54 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_FRAME_SAVED_ARG5_OFFSET

| #define CPU_STACK_FRAME_SAVED_ARG5_OFFSET 0x58 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_STACK_GROWS_UP

| #define CPU_STACK_GROWS_UP FALSE |

Does the stack grow up (toward higher addresses) or down (toward lower addresses)?

- If TRUE, then the grows upward.

- If FALSE, then the grows toward smaller addresses.

The stack grows to lower addresses on the SPARC.

◆ CPU_STACK_MINIMUM_SIZE

| #define CPU_STACK_MINIMUM_SIZE (1024*4) |

Should be large enough to run all tests.

This ensures that a "reasonable" small application should not have any problems.

This appears to be a fairly generous number for the SPARC since represents a call depth of about 20 routines based on the minimum stack frame.

◆ CPU_STRUCTURE_ALIGNMENT

| #define CPU_STRUCTURE_ALIGNMENT __attribute__ ((aligned (32))) |

The following is the variable attribute used to force alignment of critical data structures.

On some processors it may make sense to have these aligned on tighter boundaries than the minimum requirements of the compiler in order to have as much of the critical data area as possible in a cache line.

The SPARC does not appear to have particularly strict alignment requirements. This value was chosen to take advantages of caches.

◆ CPU_STRUCTURE_RETURN_ADDRESS_OFFSET

| #define CPU_STRUCTURE_RETURN_ADDRESS_OFFSET 0x40 |

This macro defines an offset into the stack frame for use in assembly.

◆ CPU_swap_u16

| #define CPU_swap_u16 | ( | value | ) | (((value&0xff) << 8) | ((value >> 8)&0xff)) |

SPARC specific method to endian swap an uint16_t.

The following routine swaps the endian format of a uint16_t.

- Parameters

-

[in] value is the value to endian swap

◆ CPU_USE_DEFERRED_FP_SWITCH

| #define CPU_USE_DEFERRED_FP_SWITCH TRUE |

Should the saving of the floating point registers be deferred until a context switch is made to another different floating point task?

- If TRUE, then the floating point context will not be stored until necessary. It will remain in the floating point registers and not disturned until another floating point task is switched to.

- If FALSE, then the floating point context is saved when a floating point task is switched out and restored when the next floating point task is restored. The state of the floating point registers between those two operations is not specified.

On the SPARC, we can disable the FPU for integer only tasks so it is safe to defer floating point context switches.

◆ CPU_USE_GENERIC_BITFIELD_DATA

| #define CPU_USE_GENERIC_BITFIELD_DATA TRUE |

The SPARC port uses the generic C algorithm for bitfield scan if the CPU model does not have a scan instruction.

Thus is needs the generic data table used by that algorithm.

◆ ISF_G1_OFFSET

| #define ISF_G1_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x0c |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_G2_OFFSET

| #define ISF_G2_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x10 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_G3_OFFSET

| #define ISF_G3_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x14 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_G4_OFFSET

| #define ISF_G4_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x18 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_G5_OFFSET

| #define ISF_G5_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x1c |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_G7_OFFSET

| #define ISF_G7_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x24 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_I0_OFFSET

| #define ISF_I0_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x28 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_I1_OFFSET

| #define ISF_I1_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x2c |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_I2_OFFSET

| #define ISF_I2_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x30 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_I3_OFFSET

| #define ISF_I3_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x34 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_I4_OFFSET

| #define ISF_I4_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x38 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_I5_OFFSET

| #define ISF_I5_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x3c |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_I6_FP_OFFSET

| #define ISF_I6_FP_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x40 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_I7_OFFSET

| #define ISF_I7_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x44 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_NPC_OFFSET

| #define ISF_NPC_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x08 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_PC_OFFSET

| #define ISF_PC_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x04 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_PSR_OFFSET

| #define ISF_PSR_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x00 |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_TPC_OFFSET

| #define ISF_TPC_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x4c |

This macro defines an offset into the ISF for use in assembly.

◆ ISF_Y_OFFSET

| #define ISF_Y_OFFSET CPU_MINIMUM_STACK_FRAME_SIZE + 0x48 |

This macro defines an offset into the ISF for use in assembly.

Variable Documentation

◆ _CPU_Trap_slot_template

| const CPU_Trap_table_entry _CPU_Trap_slot_template |

This is the set of opcodes for the instructions loaded into a trap table entry.

The routine which installs a handler is responsible for filling in the fields for the _handler address and the _vector trap type.

The constants following this structure are masks for the fields which must be filled in when the handler is installed.

Referenced by _CPU_ISR_install_raw_handler().

1.8.13

1.8.13