SPARC CPU Dependent Source. More...

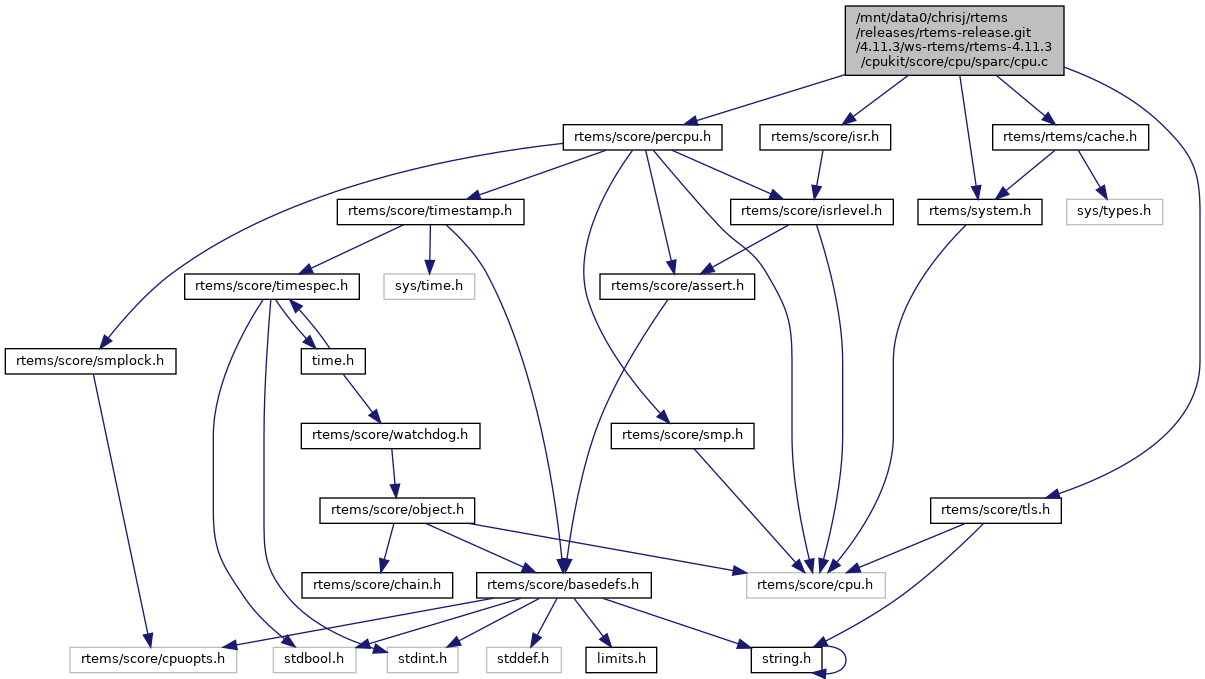

#include <rtems/system.h>#include <rtems/score/isr.h>#include <rtems/score/percpu.h>#include <rtems/score/tls.h>#include <rtems/rtems/cache.h>

Include dependency graph for cpu.c:

Macros | |

| #define | SPARC_ASSERT_OFFSET(field, off) |

| #define | SPARC_ASSERT_ISF_OFFSET(field, off) |

| #define | HIGH_BITS_MASK 0xFFFFFC00 |

| #define | HIGH_BITS_SHIFT 10 |

| #define | LOW_BITS_MASK 0x000003FF |

Functions | |

| RTEMS_STATIC_ASSERT (offsetof(Per_CPU_Control, cpu_per_cpu.isr_dispatch_disable)==SPARC_PER_CPU_ISR_DISPATCH_DISABLE, SPARC_PER_CPU_ISR_DISPATCH_DISABLE) | |

| SPARC_ASSERT_OFFSET (g5, G5) | |

| SPARC_ASSERT_OFFSET (g7, G7) | |

| RTEMS_STATIC_ASSERT (offsetof(Context_Control, l0_and_l1)==L0_OFFSET, Context_Control_offset_L0) | |

| RTEMS_STATIC_ASSERT (offsetof(Context_Control, l0_and_l1)+4==L1_OFFSET, Context_Control_offset_L1) | |

| SPARC_ASSERT_OFFSET (l2, L2) | |

| SPARC_ASSERT_OFFSET (l3, L3) | |

| SPARC_ASSERT_OFFSET (l4, L4) | |

| SPARC_ASSERT_OFFSET (l5, L5) | |

| SPARC_ASSERT_OFFSET (l6, L6) | |

| SPARC_ASSERT_OFFSET (l7, L7) | |

| SPARC_ASSERT_OFFSET (i0, I0) | |

| SPARC_ASSERT_OFFSET (i1, I1) | |

| SPARC_ASSERT_OFFSET (i2, I2) | |

| SPARC_ASSERT_OFFSET (i3, I3) | |

| SPARC_ASSERT_OFFSET (i4, I4) | |

| SPARC_ASSERT_OFFSET (i5, I5) | |

| SPARC_ASSERT_OFFSET (i6_fp, I6_FP) | |

| SPARC_ASSERT_OFFSET (i7, I7) | |

| SPARC_ASSERT_OFFSET (o6_sp, O6_SP) | |

| SPARC_ASSERT_OFFSET (o7, O7) | |

| SPARC_ASSERT_OFFSET (psr, PSR) | |

| SPARC_ASSERT_OFFSET (isr_dispatch_disable, ISR_DISPATCH_DISABLE_STACK) | |

| SPARC_ASSERT_ISF_OFFSET (psr, PSR) | |

| SPARC_ASSERT_ISF_OFFSET (pc, PC) | |

| SPARC_ASSERT_ISF_OFFSET (npc, NPC) | |

| SPARC_ASSERT_ISF_OFFSET (g1, G1) | |

| SPARC_ASSERT_ISF_OFFSET (g2, G2) | |

| SPARC_ASSERT_ISF_OFFSET (g3, G3) | |

| SPARC_ASSERT_ISF_OFFSET (g4, G4) | |

| SPARC_ASSERT_ISF_OFFSET (g5, G5) | |

| SPARC_ASSERT_ISF_OFFSET (g7, G7) | |

| SPARC_ASSERT_ISF_OFFSET (i0, I0) | |

| SPARC_ASSERT_ISF_OFFSET (i1, I1) | |

| SPARC_ASSERT_ISF_OFFSET (i2, I2) | |

| SPARC_ASSERT_ISF_OFFSET (i3, I3) | |

| SPARC_ASSERT_ISF_OFFSET (i4, I4) | |

| SPARC_ASSERT_ISF_OFFSET (i5, I5) | |

| SPARC_ASSERT_ISF_OFFSET (i6_fp, I6_FP) | |

| SPARC_ASSERT_ISF_OFFSET (i7, I7) | |

| SPARC_ASSERT_ISF_OFFSET (y, Y) | |

| SPARC_ASSERT_ISF_OFFSET (tpc, TPC) | |

| RTEMS_STATIC_ASSERT (sizeof(CPU_Interrupt_frame)==CONTEXT_CONTROL_INTERRUPT_FRAME_SIZE, CPU_Interrupt_frame_size) | |

| RTEMS_STATIC_ASSERT (sizeof(CPU_Interrupt_frame) % CPU_ALIGNMENT==0, CPU_Interrupt_frame_alignment) | |

| void | _CPU_Initialize (void) |

| CPU initialization. More... | |

| uint32_t | _CPU_ISR_Get_level (void) |

| Return the current interrupt disable level for this task in the format used by the interrupt level portion of the task mode. More... | |

| void | _CPU_ISR_install_raw_handler (uint32_t vector, proc_ptr new_handler, proc_ptr *old_handler) |

| This routine installs a "raw" interrupt handler directly into the processor's vector table. More... | |

| void | _CPU_ISR_install_vector (uint32_t vector, proc_ptr new_handler, proc_ptr *old_handler) |

| This routine installs an interrupt vector. More... | |

| void | _CPU_Context_Initialize (Context_Control *the_context, uint32_t *stack_base, uint32_t size, uint32_t new_level, void *entry_point, bool is_fp, void *tls_area) |

| Initialize the context to a state suitable for starting a task after a context restore operation. More... | |

Detailed Description

SPARC CPU Dependent Source.

Macro Definition Documentation

◆ SPARC_ASSERT_ISF_OFFSET

| #define SPARC_ASSERT_ISF_OFFSET | ( | field, | |

| off | |||

| ) |

Value:

RTEMS_STATIC_ASSERT( \

offsetof(CPU_Interrupt_frame, field) == ISF_ ## off ## _OFFSET, \

CPU_Interrupt_frame_offset_ ## field \

)

This defines the set of integer and processor state registers that must be saved during an interrupt...

Definition: cpu.h:425

◆ SPARC_ASSERT_OFFSET

| #define SPARC_ASSERT_OFFSET | ( | field, | |

| off | |||

| ) |

Value:

RTEMS_STATIC_ASSERT( \

offsetof(Context_Control, field) == off ## _OFFSET, \

Context_Control_offset_ ## field \

)

This defines the minimal set of integer and processor state registers that must be saved during a vol...

Definition: cpu.h:248

1.8.13

1.8.13