This defines the set of integer and processor state registers that must be saved during an interrupt. More...

#include <cpu.h>

Data Fields | |

| uint32_t | special_interrupt_register |

| This field is a hint that a port will have a number of integer registers that need to be saved when an interrupt occurs or when a context switch occurs at the end of an ISR. | |

| uint32_t | r1 |

| uint32_t | r2 |

| uint32_t | r3 |

| uint32_t | r4 |

| uint32_t | r5 |

| uint32_t | r6 |

| uint32_t | r7 |

| uint32_t | r8 |

| uint32_t | r9 |

| uint32_t | r10 |

| uint32_t | ra |

| uint32_t | ba |

| uint32_t | ea |

| uint32_t | vecnum |

| __MIPS_REGISTER_TYPE | r0 |

| __MIPS_REGISTER_TYPE | at |

| __MIPS_REGISTER_TYPE | v0 |

| __MIPS_REGISTER_TYPE | v1 |

| __MIPS_REGISTER_TYPE | a0 |

| __MIPS_REGISTER_TYPE | a1 |

| __MIPS_REGISTER_TYPE | a2 |

| __MIPS_REGISTER_TYPE | a3 |

| __MIPS_REGISTER_TYPE | t0 |

| __MIPS_REGISTER_TYPE | t1 |

| __MIPS_REGISTER_TYPE | t2 |

| __MIPS_REGISTER_TYPE | t3 |

| __MIPS_REGISTER_TYPE | t4 |

| __MIPS_REGISTER_TYPE | t5 |

| __MIPS_REGISTER_TYPE | t6 |

| __MIPS_REGISTER_TYPE | t7 |

| __MIPS_REGISTER_TYPE | s0 |

| __MIPS_REGISTER_TYPE | s1 |

| __MIPS_REGISTER_TYPE | s2 |

| __MIPS_REGISTER_TYPE | s3 |

| __MIPS_REGISTER_TYPE | s4 |

| __MIPS_REGISTER_TYPE | s5 |

| __MIPS_REGISTER_TYPE | s6 |

| __MIPS_REGISTER_TYPE | s7 |

| __MIPS_REGISTER_TYPE | t8 |

| __MIPS_REGISTER_TYPE | t9 |

| __MIPS_REGISTER_TYPE | k0 |

| __MIPS_REGISTER_TYPE | k1 |

| __MIPS_REGISTER_TYPE | gp |

| __MIPS_REGISTER_TYPE | sp |

| __MIPS_REGISTER_TYPE | fp |

| __MIPS_REGISTER_TYPE | ra |

| __MIPS_REGISTER_TYPE | c0_sr |

| __MIPS_REGISTER_TYPE | mdlo |

| __MIPS_REGISTER_TYPE | mdhi |

| __MIPS_REGISTER_TYPE | badvaddr |

| __MIPS_REGISTER_TYPE | cause |

| __MIPS_REGISTER_TYPE | epc |

| __MIPS_FPU_REGISTER_TYPE | f0 |

| __MIPS_FPU_REGISTER_TYPE | f1 |

| __MIPS_FPU_REGISTER_TYPE | f2 |

| __MIPS_FPU_REGISTER_TYPE | f3 |

| __MIPS_FPU_REGISTER_TYPE | f4 |

| __MIPS_FPU_REGISTER_TYPE | f5 |

| __MIPS_FPU_REGISTER_TYPE | f6 |

| __MIPS_FPU_REGISTER_TYPE | f7 |

| __MIPS_FPU_REGISTER_TYPE | f8 |

| __MIPS_FPU_REGISTER_TYPE | f9 |

| __MIPS_FPU_REGISTER_TYPE | f10 |

| __MIPS_FPU_REGISTER_TYPE | f11 |

| __MIPS_FPU_REGISTER_TYPE | f12 |

| __MIPS_FPU_REGISTER_TYPE | f13 |

| __MIPS_FPU_REGISTER_TYPE | f14 |

| __MIPS_FPU_REGISTER_TYPE | f15 |

| __MIPS_FPU_REGISTER_TYPE | f16 |

| __MIPS_FPU_REGISTER_TYPE | f17 |

| __MIPS_FPU_REGISTER_TYPE | f18 |

| __MIPS_FPU_REGISTER_TYPE | f19 |

| __MIPS_FPU_REGISTER_TYPE | f20 |

| __MIPS_FPU_REGISTER_TYPE | f21 |

| __MIPS_FPU_REGISTER_TYPE | f22 |

| __MIPS_FPU_REGISTER_TYPE | f23 |

| __MIPS_FPU_REGISTER_TYPE | f24 |

| __MIPS_FPU_REGISTER_TYPE | f25 |

| __MIPS_FPU_REGISTER_TYPE | f26 |

| __MIPS_FPU_REGISTER_TYPE | f27 |

| __MIPS_FPU_REGISTER_TYPE | f28 |

| __MIPS_FPU_REGISTER_TYPE | f29 |

| __MIPS_FPU_REGISTER_TYPE | f30 |

| __MIPS_FPU_REGISTER_TYPE | f31 |

| __MIPS_REGISTER_TYPE | fcsr |

| __MIPS_REGISTER_TYPE | feir |

| __MIPS_REGISTER_TYPE | tlbhi |

| __MIPS_REGISTER_TYPE | inx |

| __MIPS_REGISTER_TYPE | rand |

| __MIPS_REGISTER_TYPE | ctxt |

| __MIPS_REGISTER_TYPE | exctype |

| __MIPS_REGISTER_TYPE | mode |

| __MIPS_REGISTER_TYPE | prid |

| __MIPS_REGISTER_TYPE | tar |

| uint32_t | stacklink |

| uint32_t | calleeLr |

| uint32_t | gpr0 |

| uint32_t | gpr2 |

| uint32_t | gpr3 |

| uint32_t | gpr4 |

| uint32_t | gpr5 |

| uint32_t | gpr6 |

| uint32_t | gpr7 |

| uint32_t | gpr8 |

| uint32_t | gpr9 |

| uint32_t | gpr10 |

| uint32_t | gpr11 |

| uint32_t | gpr12 |

| uint32_t | gpr13 |

| uint32_t | gpr28 |

| uint32_t | gpr29 |

| uint32_t | gpr30 |

| uint32_t | gpr31 |

| uint32_t | cr |

| uint32_t | ctr |

| uint32_t | xer |

| uint32_t | lr |

| uint32_t | pc |

| This is the offset of the XXX on an ISF. More... | |

| uint32_t | msr |

| uint32_t | pad [3] |

| CPU_Minimum_stack_frame | Stack_frame |

| On an interrupt, we must save the minimum stack frame. More... | |

| uint32_t | psr |

| This is the offset of the PSR on an ISF. More... | |

| uint32_t | npc |

| This is the offset of the XXX on an ISF. More... | |

| uint32_t | g1 |

| This is the offset of the g1 register on an ISF. More... | |

| uint32_t | g2 |

| This is the offset of the g2 register on an ISF. More... | |

| uint32_t | g3 |

| This is the offset of the g3 register on an ISF. More... | |

| uint32_t | g4 |

| This is the offset of the g4 register on an ISF. More... | |

| uint32_t | g5 |

| This is the offset of the g5 register on an ISF. More... | |

| uint32_t | reserved_for_alignment |

| This is the offset is reserved for alignment on an ISF. More... | |

| uint32_t | g7 |

| This is the offset of the g7 register on an ISF. More... | |

| uint32_t | i0 |

| This is the offset of the i0 register on an ISF. More... | |

| uint32_t | i1 |

| This is the offset of the i1 register on an ISF. More... | |

| uint32_t | i2 |

| This is the offset of the i2 register on an ISF. More... | |

| uint32_t | i3 |

| This is the offset of the i3 register on an ISF. More... | |

| uint32_t | i4 |

| This is the offset of the i4 register on an ISF. More... | |

| uint32_t | i5 |

| This is the offset of the i5 register on an ISF. More... | |

| uint32_t | i6_fp |

| This is the offset of the i6 register on an ISF. More... | |

| uint32_t | i7 |

| This is the offset of the i7 register on an ISF. More... | |

| uint32_t | y |

| This is the offset of the y register on an ISF. More... | |

| uint32_t | tpc |

| This is the offset of the tpc register on an ISF. More... | |

| uint64_t | tstate |

| uint64_t | tpc |

| uint64_t | tnpc |

| uint64_t | pil |

| uint64_t | y |

| uint64_t | g1 |

| uint64_t | g2 |

| uint64_t | g3 |

| uint64_t | g4 |

| uint64_t | g5 |

| uint64_t | g6 |

| uint64_t | g7 |

| uint64_t | o0 |

| uint64_t | o1 |

| uint64_t | o2 |

| uint64_t | o3 |

| uint64_t | o4 |

| uint64_t | o5 |

| uint64_t | o6_sp |

| uint64_t | o7 |

| uint64_t | tvec |

Detailed Description

This defines the set of integer and processor state registers that must be saved during an interrupt.

Interrupt stack frame (ISF).

This set does not include any which are in Context_Control.

Context saved on stack for an interrupt.

NOTE: The PSR, PC, and NPC are only saved in this structure for the benefit of the user's handler.

Field Documentation

◆ g1

| uint32_t CPU_Interrupt_frame::g1 |

This is the offset of the g1 register on an ISF.

◆ g2

| uint32_t CPU_Interrupt_frame::g2 |

This is the offset of the g2 register on an ISF.

◆ g3

| uint32_t CPU_Interrupt_frame::g3 |

This is the offset of the g3 register on an ISF.

◆ g4

| uint32_t CPU_Interrupt_frame::g4 |

This is the offset of the g4 register on an ISF.

◆ g5

| uint32_t CPU_Interrupt_frame::g5 |

This is the offset of the g5 register on an ISF.

◆ g7

| uint32_t CPU_Interrupt_frame::g7 |

This is the offset of the g7 register on an ISF.

◆ i0

| uint32_t CPU_Interrupt_frame::i0 |

This is the offset of the i0 register on an ISF.

◆ i1

| uint32_t CPU_Interrupt_frame::i1 |

This is the offset of the i1 register on an ISF.

◆ i2

| uint32_t CPU_Interrupt_frame::i2 |

This is the offset of the i2 register on an ISF.

◆ i3

| uint32_t CPU_Interrupt_frame::i3 |

This is the offset of the i3 register on an ISF.

◆ i4

| uint32_t CPU_Interrupt_frame::i4 |

This is the offset of the i4 register on an ISF.

◆ i5

| uint32_t CPU_Interrupt_frame::i5 |

This is the offset of the i5 register on an ISF.

◆ i6_fp

| uint32_t CPU_Interrupt_frame::i6_fp |

This is the offset of the i6 register on an ISF.

◆ i7

| uint32_t CPU_Interrupt_frame::i7 |

This is the offset of the i7 register on an ISF.

◆ npc

| uint32_t CPU_Interrupt_frame::npc |

This is the offset of the XXX on an ISF.

◆ pc

| uint32_t CPU_Interrupt_frame::pc |

This is the offset of the XXX on an ISF.

◆ psr

| uint32_t CPU_Interrupt_frame::psr |

This is the offset of the PSR on an ISF.

◆ reserved_for_alignment

| uint32_t CPU_Interrupt_frame::reserved_for_alignment |

This is the offset is reserved for alignment on an ISF.

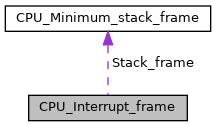

◆ Stack_frame

| CPU_Minimum_stack_frame CPU_Interrupt_frame::Stack_frame |

On an interrupt, we must save the minimum stack frame.

◆ tpc

| uint32_t CPU_Interrupt_frame::tpc |

This is the offset of the tpc register on an ISF.

◆ y

| uint32_t CPU_Interrupt_frame::y |

This is the offset of the y register on an ISF.

The documentation for this struct was generated from the following file:

- /mnt/data0/chrisj/rtems/releases/rtems-release.git/4.11.3/ws-rtems/rtems-4.11.3/cpukit/score/cpu/avr/rtems/score/cpu.h

1.8.13

1.8.13