Watchdog Timer Handling. More...

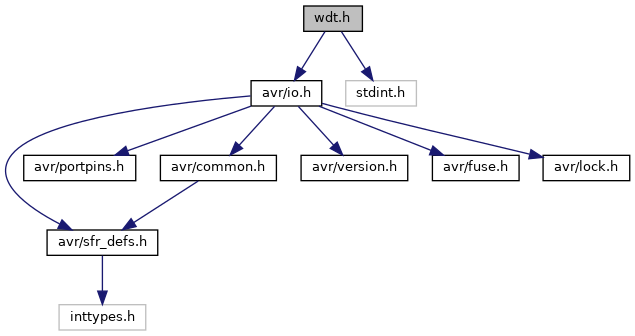

Include dependency graph for wdt.h:

Go to the source code of this file.

Macros | |

| #define | wdt_reset() __asm__ __volatile__ ("wdr") |

| Watchdog Timer Reset. More... | |

| #define | _WD_PS3_MASK 0x00 |

| #define | _WD_CONTROL_REG WDTCR |

| #define | _WD_CHANGE_BIT WDCE |

| #define | wdt_enable(value) |

Enable the watchdog timer, configuring it for expiry after timeout (which is a combination of the WDP0 through WDP2 bits to write into the WDTCR register; For those devices that have a WDTCSR register, it uses the combination of the WDP0 through WDP3 bits). More... | |

| #define | wdt_disable() |

| Disable the watchdog timer, if possible. More... | |

| #define | WDTO_15MS 0 |

| Symbolic constants for the watchdog timeout. More... | |

| #define | WDTO_30MS 1 |

| #define | WDTO_60MS 2 |

| #define | WDTO_120MS 3 |

| #define | WDTO_250MS 4 |

| #define | WDTO_500MS 5 |

| #define | WDTO_1S 6 |

| #define | WDTO_2S 7 |

Detailed Description

Watchdog Timer Handling.

1.8.13

1.8.13