#include <avr/sfr_defs.h>

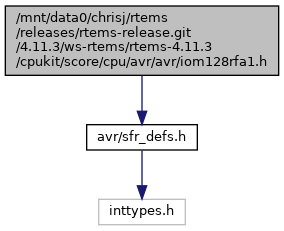

Include dependency graph for iom128rfa1.h:

Go to the source code of this file.

Macros | |

| #define | _AVR_IOXXX_H_ "iom128rfa1.h" |

| #define | _MMIO_BYTE_STRUCT(mem_addr, type) (*(volatile type *)(mem_addr)) |

| #define | _SFR_IO8_STRUCT(io_addr, type) _MMIO_BYTE_STRUCT((io_addr) + 0x20, type) |

| #define | _SFR_MEM8_STRUCT(io_addr, type) _MMIO_BYTE_STRUCT((io_addr), type) |

| #define | PINA _SFR_IO8(0x00) |

| #define | PINA0 0 |

| #define | PINA1 1 |

| #define | PINA2 2 |

| #define | PINA3 3 |

| #define | PINA4 4 |

| #define | PINA5 5 |

| #define | PINA6 6 |

| #define | PINA7 7 |

| #define | DDRA _SFR_IO8(0x01) |

| #define | DDA0 0 |

| #define | DDA1 1 |

| #define | DDA2 2 |

| #define | DDA3 3 |

| #define | DDA4 4 |

| #define | DDA5 5 |

| #define | DDA6 6 |

| #define | DDA7 7 |

| #define | PORTA _SFR_IO8(0x02) |

| #define | PORTA0 0 |

| #define | PA0 0 |

| #define | PORTA1 1 |

| #define | PA1 1 |

| #define | PORTA2 2 |

| #define | PA2 2 |

| #define | PORTA3 3 |

| #define | PA3 3 |

| #define | PORTA4 4 |

| #define | PA4 4 |

| #define | PORTA5 5 |

| #define | PA5 5 |

| #define | PORTA6 6 |

| #define | PA6 6 |

| #define | PORTA7 7 |

| #define | PA7 7 |

| #define | PINB _SFR_IO8(0x03) |

| #define | PINB0 0 |

| #define | PINB1 1 |

| #define | PINB2 2 |

| #define | PINB3 3 |

| #define | PINB4 4 |

| #define | PINB5 5 |

| #define | PINB6 6 |

| #define | PINB7 7 |

| #define | DDRB _SFR_IO8(0x04) |

| #define | DDB0 0 |

| #define | DDB1 1 |

| #define | DDB2 2 |

| #define | DDB3 3 |

| #define | DDB4 4 |

| #define | DDB5 5 |

| #define | DDB6 6 |

| #define | DDB7 7 |

| #define | PORTB _SFR_IO8(0x05) |

| #define | PORTB0 0 |

| #define | PB0 0 |

| #define | PORTB1 1 |

| #define | PB1 1 |

| #define | PORTB2 2 |

| #define | PB2 2 |

| #define | PORTB3 3 |

| #define | PB3 3 |

| #define | PORTB4 4 |

| #define | PB4 4 |

| #define | PORTB5 5 |

| #define | PB5 5 |

| #define | PORTB6 6 |

| #define | PB6 6 |

| #define | PORTB7 7 |

| #define | PB7 7 |

| #define | PINC _SFR_IO8(0x06) |

| #define | PINC0 0 |

| #define | PINC1 1 |

| #define | PINC2 2 |

| #define | PINC3 3 |

| #define | PINC4 4 |

| #define | PINC5 5 |

| #define | PINC6 6 |

| #define | PINC7 7 |

| #define | DDRC _SFR_IO8(0x07) |

| #define | DDC0 0 |

| #define | DDC1 1 |

| #define | DDC2 2 |

| #define | DDC3 3 |

| #define | DDC4 4 |

| #define | DDC5 5 |

| #define | DDC6 6 |

| #define | DDC7 7 |

| #define | PORTC _SFR_IO8(0x08) |

| #define | PORTC0 0 |

| #define | PC0 0 |

| #define | PORTC1 1 |

| #define | PC1 1 |

| #define | PORTC2 2 |

| #define | PC2 2 |

| #define | PORTC3 3 |

| #define | PC3 3 |

| #define | PORTC4 4 |

| #define | PC4 4 |

| #define | PORTC5 5 |

| #define | PC5 5 |

| #define | PORTC6 6 |

| #define | PC6 6 |

| #define | PORTC7 7 |

| #define | PC7 7 |

| #define | PIND _SFR_IO8(0x09) |

| #define | PIND0 0 |

| #define | PIND1 1 |

| #define | PIND2 2 |

| #define | PIND3 3 |

| #define | PIND4 4 |

| #define | PIND5 5 |

| #define | PIND6 6 |

| #define | PIND7 7 |

| #define | DDRD _SFR_IO8(0x0A) |

| #define | DDD0 0 |

| #define | DDD1 1 |

| #define | DDD2 2 |

| #define | DDD3 3 |

| #define | DDD4 4 |

| #define | DDD5 5 |

| #define | DDD6 6 |

| #define | DDD7 7 |

| #define | PORTD _SFR_IO8(0x0B) |

| #define | PORTD0 0 |

| #define | PD0 0 |

| #define | PORTD1 1 |

| #define | PD1 1 |

| #define | PORTD2 2 |

| #define | PD2 2 |

| #define | PORTD3 3 |

| #define | PD3 3 |

| #define | PORTD4 4 |

| #define | PD4 4 |

| #define | PORTD5 5 |

| #define | PD5 5 |

| #define | PORTD6 6 |

| #define | PD6 6 |

| #define | PORTD7 7 |

| #define | PD7 7 |

| #define | PINE _SFR_IO8(0x0C) |

| #define | PINE0 0 |

| #define | PINE1 1 |

| #define | PINE2 2 |

| #define | PINE3 3 |

| #define | PINE4 4 |

| #define | PINE5 5 |

| #define | PINE6 6 |

| #define | PINE7 7 |

| #define | DDRE _SFR_IO8(0x0D) |

| #define | DDE0 0 |

| #define | DDE1 1 |

| #define | DDE2 2 |

| #define | DDE3 3 |

| #define | DDE4 4 |

| #define | DDE5 5 |

| #define | DDE6 6 |

| #define | DDE7 7 |

| #define | PORTE _SFR_IO8(0x0E) |

| #define | PORTE0 0 |

| #define | PE0 0 |

| #define | PORTE1 1 |

| #define | PE1 1 |

| #define | PORTE2 2 |

| #define | PE2 2 |

| #define | PORTE3 3 |

| #define | PE3 3 |

| #define | PORTE4 4 |

| #define | PE4 4 |

| #define | PORTE5 5 |

| #define | PE5 5 |

| #define | PORTE6 6 |

| #define | PE6 6 |

| #define | PORTE7 7 |

| #define | PE7 7 |

| #define | PINF _SFR_IO8(0x0F) |

| #define | PINF0 0 |

| #define | PINF1 1 |

| #define | PINF2 2 |

| #define | PINF3 3 |

| #define | PINF4 4 |

| #define | PINF5 5 |

| #define | PINF6 6 |

| #define | PINF7 7 |

| #define | DDRF _SFR_IO8(0x10) |

| #define | DDF0 0 |

| #define | DDF1 1 |

| #define | DDF2 2 |

| #define | DDF3 3 |

| #define | DDF4 4 |

| #define | DDF5 5 |

| #define | DDF6 6 |

| #define | DDF7 7 |

| #define | PORTF _SFR_IO8(0x11) |

| #define | PORTF0 0 |

| #define | PF0 0 |

| #define | PORTF1 1 |

| #define | PF1 1 |

| #define | PORTF2 2 |

| #define | PF2 2 |

| #define | PORTF3 3 |

| #define | PF3 3 |

| #define | PORTF4 4 |

| #define | PF4 4 |

| #define | PORTF5 5 |

| #define | PF5 5 |

| #define | PORTF6 6 |

| #define | PF6 6 |

| #define | PORTF7 7 |

| #define | PF7 7 |

| #define | PING _SFR_IO8(0x12) |

| #define | PING0 0 |

| #define | PING1 1 |

| #define | PING2 2 |

| #define | PING3 3 |

| #define | PING4 4 |

| #define | PING5 5 |

| #define | DDRG _SFR_IO8(0x13) |

| #define | DDG0 0 |

| #define | DDG1 1 |

| #define | DDG2 2 |

| #define | DDG3 3 |

| #define | DDG4 4 |

| #define | DDG5 5 |

| #define | PORTG _SFR_IO8(0x14) |

| #define | PORTG0 0 |

| #define | PG0 0 |

| #define | PORTG1 1 |

| #define | PG1 1 |

| #define | PORTG2 2 |

| #define | PG2 2 |

| #define | PORTG3 3 |

| #define | PG3 3 |

| #define | PORTG4 4 |

| #define | PG4 4 |

| #define | PORTG5 5 |

| #define | PG5 5 |

| #define | TIFR0 _SFR_IO8(0x15) |

| #define | TIFR0_struct _SFR_IO8_STRUCT(0x15, struct __reg_TIFR0) |

| #define | TOV0 0 |

| #define | OCF0A 1 |

| #define | OCF0B 2 |

| #define | TIFR1 _SFR_IO8(0x16) |

| #define | TIFR1_struct _SFR_IO8_STRUCT(0x16, struct __reg_TIFR1) |

| #define | TOV1 0 |

| #define | OCF1A 1 |

| #define | OCF1B 2 |

| #define | OCF1C 3 |

| #define | ICF1 5 |

| #define | TIFR2 _SFR_IO8(0x17) |

| #define | TIFR2_struct _SFR_IO8_STRUCT(0x17, struct __reg_TIFR2) |

| #define | TOV2 0 |

| #define | OCF2A 1 |

| #define | OCF2B 2 |

| #define | TIFR3 _SFR_IO8(0x18) |

| #define | TIFR3_struct _SFR_IO8_STRUCT(0x18, struct __reg_TIFR3) |

| #define | TOV3 0 |

| #define | OCF3A 1 |

| #define | OCF3B 2 |

| #define | OCF3C 3 |

| #define | ICF3 5 |

| #define | TIFR4 _SFR_IO8(0x19) |

| #define | TIFR4_struct _SFR_IO8_STRUCT(0x19, struct __reg_TIFR4) |

| #define | TOV4 0 |

| #define | OCF4A 1 |

| #define | OCF4B 2 |

| #define | OCF4C 3 |

| #define | ICF4 5 |

| #define | TIFR5 _SFR_IO8(0x1A) |

| #define | TIFR5_struct _SFR_IO8_STRUCT(0x1a, struct __reg_TIFR5) |

| #define | TOV5 0 |

| #define | OCF5A 1 |

| #define | OCF5B 2 |

| #define | OCF5C 3 |

| #define | ICF5 5 |

| #define | PCIFR _SFR_IO8(0x1B) |

| #define | PCIFR_struct _SFR_IO8_STRUCT(0x1b, struct __reg_PCIFR) |

| #define | PCIF0 0 |

| #define | PCIF1 1 |

| #define | PCIF2 2 |

| #define | EIFR _SFR_IO8(0x1C) |

| #define | EIFR_struct _SFR_IO8_STRUCT(0x1c, struct __reg_EIFR) |

| #define | INTF0 0 |

| #define | INTF1 1 |

| #define | INTF2 2 |

| #define | INTF3 3 |

| #define | INTF4 4 |

| #define | INTF5 5 |

| #define | INTF6 6 |

| #define | INTF7 7 |

| #define | EIMSK _SFR_IO8(0x1D) |

| #define | EIMSK_struct _SFR_IO8_STRUCT(0x1d, struct __reg_EIMSK) |

| #define | INT0 0 |

| #define | INT1 1 |

| #define | INT2 2 |

| #define | INT3 3 |

| #define | INT4 4 |

| #define | INT5 5 |

| #define | INT6 6 |

| #define | INT7 7 |

| #define | GPIOR0 _SFR_IO8(0x1E) |

| #define | GPIOR0_struct _SFR_IO8_STRUCT(0x1e, struct __reg_GPIOR0) |

| #define | GPIOR00 0 |

| #define | GPIOR01 1 |

| #define | GPIOR02 2 |

| #define | GPIOR03 3 |

| #define | GPIOR04 4 |

| #define | GPIOR05 5 |

| #define | GPIOR06 6 |

| #define | GPIOR07 7 |

| #define | __EEPROM_REG_LOCATIONS__ 1F2021 |

| #define | EECR _SFR_IO8(0x1F) |

| #define | EECR_struct _SFR_IO8_STRUCT(0x1f, struct __reg_EECR) |

| #define | EERE 0 |

| #define | EEPE 1 |

| #define | EEMPE 2 |

| #define | EERIE 3 |

| #define | EEPM0 4 |

| #define | EEPM1 5 |

| #define | EEDR _SFR_IO8(0x20) |

| #define | EEDR0 0 |

| #define | EEDR1 1 |

| #define | EEDR2 2 |

| #define | EEDR3 3 |

| #define | EEDR4 4 |

| #define | EEDR5 5 |

| #define | EEDR6 6 |

| #define | EEDR7 7 |

| #define | EEAR _SFR_IO16(0x21) |

| #define | EEARL _SFR_IO8(0x21) |

| #define | EEARH _SFR_IO8(0x22) |

| #define | GTCCR _SFR_IO8(0x23) |

| #define | GTCCR_struct _SFR_IO8_STRUCT(0x23, struct __reg_GTCCR) |

| #define | PSRSYNC 0 |

| #define | PSR10 0 |

| #define | PSRASY 1 |

| #define | PSR2 1 |

| #define | TSM 7 |

| #define | TCCR0A _SFR_IO8(0x24) |

| #define | TCCR0A_struct _SFR_IO8_STRUCT(0x24, struct __reg_TCCR0A) |

| #define | WGM00 0 |

| #define | WGM01 1 |

| #define | COM0B0 4 |

| #define | COM0B1 5 |

| #define | COM0A0 6 |

| #define | COM0A1 7 |

| #define | TCCR0B _SFR_IO8(0x25) |

| #define | TCCR0B_struct _SFR_IO8_STRUCT(0x25, struct __reg_TCCR0B) |

| #define | CS00 0 |

| #define | CS01 1 |

| #define | CS02 2 |

| #define | WGM02 3 |

| #define | FOC0B 6 |

| #define | FOC0A 7 |

| #define | TCNT0 _SFR_IO8(0x26) |

| #define | TCNT0_0 0 |

| #define | TCNT0_1 1 |

| #define | TCNT0_2 2 |

| #define | TCNT0_3 3 |

| #define | TCNT0_4 4 |

| #define | TCNT0_5 5 |

| #define | TCNT0_6 6 |

| #define | TCNT0_7 7 |

| #define | OCR0A _SFR_IO8(0x27) |

| #define | OCR0A_0 0 |

| #define | OCR0A_1 1 |

| #define | OCR0A_2 2 |

| #define | OCR0A_3 3 |

| #define | OCR0A_4 4 |

| #define | OCR0A_5 5 |

| #define | OCR0A_6 6 |

| #define | OCR0A_7 7 |

| #define | OCR0B _SFR_IO8(0x28) |

| #define | OCR0B_0 0 |

| #define | OCR0B_1 1 |

| #define | OCR0B_2 2 |

| #define | OCR0B_3 3 |

| #define | OCR0B_4 4 |

| #define | OCR0B_5 5 |

| #define | OCR0B_6 6 |

| #define | OCR0B_7 7 |

| #define | GPIOR1 _SFR_IO8(0x2A) |

| #define | GPIOR1_struct _SFR_IO8_STRUCT(0x2a, struct __reg_GPIOR1) |

| #define | GPIOR10 0 |

| #define | GPIOR11 1 |

| #define | GPIOR12 2 |

| #define | GPIOR13 3 |

| #define | GPIOR14 4 |

| #define | GPIOR15 5 |

| #define | GPIOR16 6 |

| #define | GPIOR17 7 |

| #define | GPIOR2 _SFR_IO8(0x2B) |

| #define | GPIOR2_struct _SFR_IO8_STRUCT(0x2b, struct __reg_GPIOR2) |

| #define | GPIOR20 0 |

| #define | GPIOR21 1 |

| #define | GPIOR22 2 |

| #define | GPIOR23 3 |

| #define | GPIOR24 4 |

| #define | GPIOR25 5 |

| #define | GPIOR26 6 |

| #define | GPIOR27 7 |

| #define | SPCR _SFR_IO8(0x2C) |

| #define | SPCR_struct _SFR_IO8_STRUCT(0x2c, struct __reg_SPCR) |

| #define | SPR0 0 |

| #define | SPR1 1 |

| #define | CPHA 2 |

| #define | CPOL 3 |

| #define | MSTR 4 |

| #define | DORD 5 |

| #define | SPE 6 |

| #define | SPIE 7 |

| #define | SPSR _SFR_IO8(0x2D) |

| #define | SPSR_struct _SFR_IO8_STRUCT(0x2d, struct __reg_SPSR) |

| #define | SPI2X 0 |

| #define | WCOL 6 |

| #define | SPIF 7 |

| #define | SPDR _SFR_IO8(0x2E) |

| #define | SPDR0 0 |

| #define | SPDR1 1 |

| #define | SPDR2 2 |

| #define | SPDR3 3 |

| #define | SPDR4 4 |

| #define | SPDR5 5 |

| #define | SPDR6 6 |

| #define | SPDR7 7 |

| #define | ACSR _SFR_IO8(0x30) |

| #define | ACSR_struct _SFR_IO8_STRUCT(0x30, struct __reg_ACSR) |

| #define | ACIS0 0 |

| #define | ACIS1 1 |

| #define | ACIC 2 |

| #define | ACIE 3 |

| #define | ACI 4 |

| #define | ACO 5 |

| #define | ACBG 6 |

| #define | ACD 7 |

| #define | OCDR _SFR_IO8(0x31) |

| #define | OCDR_struct _SFR_IO8_STRUCT(0x31, struct __reg_OCDR) |

| #define | OCDR0 0 |

| #define | OCDR1 1 |

| #define | OCDR2 2 |

| #define | OCDR3 3 |

| #define | OCDR4 4 |

| #define | OCDR5 5 |

| #define | OCDR6 6 |

| #define | OCDR7 7 |

| #define | IDRD 7 |

| #define | SMCR _SFR_IO8(0x33) |

| #define | SMCR_struct _SFR_IO8_STRUCT(0x33, struct __reg_SMCR) |

| #define | SE 0 |

| #define | SM0 1 |

| #define | SM1 2 |

| #define | SM2 3 |

| #define | MCUSR _SFR_IO8(0x34) |

| #define | MCUSR_struct _SFR_IO8_STRUCT(0x34, struct __reg_MCUSR) |

| #define | PORF 0 |

| #define | EXTRF 1 |

| #define | BORF 2 |

| #define | WDRF 3 |

| #define | JTRF 4 |

| #define | MCUCR _SFR_IO8(0x35) |

| #define | MCUCR_struct _SFR_IO8_STRUCT(0x35, struct __reg_MCUCR) |

| #define | IVCE 0 |

| #define | IVSEL 1 |

| #define | PUD 4 |

| #define | JTD 7 |

| #define | SPMCSR _SFR_IO8(0x37) |

| #define | SPMCSR_struct _SFR_IO8_STRUCT(0x37, struct __reg_SPMCSR) |

| #define | SPMEN 0 |

| #define | PGERS 1 |

| #define | PGWRT 2 |

| #define | BLBSET 3 |

| #define | RWWSRE 4 |

| #define | SIGRD 5 |

| #define | RWWSB 6 |

| #define | SPMIE 7 |

| #define | RAMPZ _SFR_IO8(0x3B) |

| #define | RAMPZ_struct _SFR_IO8_STRUCT(0x3b, struct __reg_RAMPZ) |

| #define | RAMPZ0 0 |

| #define | RAMPZ1 1 |

| #define | SP _SFR_IO16(0x3D) |

| #define | SPL _SFR_IO8(0x3D) |

| #define | SPH _SFR_IO8(0x3E) |

| #define | SREG _SFR_IO8(0x3F) |

| #define | SREG_struct _SFR_IO8_STRUCT(0x3f, struct __reg_SREG) |

| #define | SREG_C 0 |

| #define | SREG_Z 1 |

| #define | SREG_N 2 |

| #define | SREG_V 3 |

| #define | SREG_S 4 |

| #define | SREG_H 5 |

| #define | SREG_T 6 |

| #define | SREG_I 7 |

| #define | WDTCSR _SFR_MEM8(0x60) |

| #define | WDTCSR_struct _SFR_MEM8_STRUCT(0x60, struct __reg_WDTCSR) |

| #define | WDP0 0 |

| #define | WDP1 1 |

| #define | WDP2 2 |

| #define | WDE 3 |

| #define | WDCE 4 |

| #define | WDP3 5 |

| #define | WDIE 6 |

| #define | WDIF 7 |

| #define | CLKPR _SFR_MEM8(0x61) |

| #define | CLKPR_struct _SFR_MEM8_STRUCT(0x61, struct __reg_CLKPR) |

| #define | CLKPS0 0 |

| #define | CLKPS1 1 |

| #define | CLKPS2 2 |

| #define | CLKPS3 3 |

| #define | CLKPCE 7 |

| #define | PRR2 _SFR_MEM8(0x63) |

| #define | PRR2_struct _SFR_MEM8_STRUCT(0x63, struct __reg_PRR2) |

| #define | PRRAM0 0 |

| #define | PRRAM1 1 |

| #define | PRRAM2 2 |

| #define | PRRAM3 3 |

| #define | PRR0 _SFR_MEM8(0x64) |

| #define | PRR0_struct _SFR_MEM8_STRUCT(0x64, struct __reg_PRR0) |

| #define | PRADC 0 |

| #define | PRUSART0 1 |

| #define | PRSPI 2 |

| #define | PRTIM1 3 |

| #define | PRPGA 4 |

| #define | PRTIM0 5 |

| #define | PRTIM2 6 |

| #define | PRTWI 7 |

| #define | PRR1 _SFR_MEM8(0x65) |

| #define | PRR1_struct _SFR_MEM8_STRUCT(0x65, struct __reg_PRR1) |

| #define | PRUSART1 0 |

| #define | PRUSART2 1 |

| #define | PRUSART3 2 |

| #define | PRTIM3 3 |

| #define | PRTIM4 4 |

| #define | PRTIM5 5 |

| #define | PRTRX24 6 |

| #define | OSCCAL _SFR_MEM8(0x66) |

| #define | OSCCAL_struct _SFR_MEM8_STRUCT(0x66, struct __reg_OSCCAL) |

| #define | CAL0 0 |

| #define | CAL1 1 |

| #define | CAL2 2 |

| #define | CAL3 3 |

| #define | CAL4 4 |

| #define | CAL5 5 |

| #define | CAL6 6 |

| #define | CAL7 7 |

| #define | BGCR _SFR_MEM8(0x67) |

| #define | BGCR_struct _SFR_MEM8_STRUCT(0x67, struct __reg_BGCR) |

| #define | BGCAL0 0 |

| #define | BGCAL1 1 |

| #define | BGCAL2 2 |

| #define | BGCAL_FINE0 3 |

| #define | BGCAL_FINE1 4 |

| #define | BGCAL_FINE2 5 |

| #define | BGCAL_FINE3 6 |

| #define | PCICR _SFR_MEM8(0x68) |

| #define | PCICR_struct _SFR_MEM8_STRUCT(0x68, struct __reg_PCICR) |

| #define | PCIE0 0 |

| #define | PCIE1 1 |

| #define | PCIE2 2 |

| #define | EICRA _SFR_MEM8(0x69) |

| #define | EICRA_struct _SFR_MEM8_STRUCT(0x69, struct __reg_EICRA) |

| #define | ISC00 0 |

| #define | ISC01 1 |

| #define | ISC10 2 |

| #define | ISC11 3 |

| #define | ISC20 4 |

| #define | ISC21 5 |

| #define | ISC30 6 |

| #define | ISC31 7 |

| #define | EICRB _SFR_MEM8(0x6A) |

| #define | EICRB_struct _SFR_MEM8_STRUCT(0x6a, struct __reg_EICRB) |

| #define | ISC40 0 |

| #define | ISC41 1 |

| #define | ISC50 2 |

| #define | ISC51 3 |

| #define | ISC60 4 |

| #define | ISC61 5 |

| #define | ISC70 6 |

| #define | ISC71 7 |

| #define | PCMSK0 _SFR_MEM8(0x6B) |

| #define | PCINT0 0 |

| #define | PCINT1 1 |

| #define | PCINT2 2 |

| #define | PCINT3 3 |

| #define | PCINT4 4 |

| #define | PCINT5 5 |

| #define | PCINT6 6 |

| #define | PCINT7 7 |

| #define | PCMSK1 _SFR_MEM8(0x6C) |

| #define | PCMSK1_struct _SFR_MEM8_STRUCT(0x6c, struct __reg_PCMSK1) |

| #define | PCINT8 0 |

| #define | PCINT9 1 |

| #define | PCINT10 2 |

| #define | PCINT11 3 |

| #define | PCINT12 4 |

| #define | PCINT13 5 |

| #define | PCINT14 6 |

| #define | PCINT15 7 |

| #define | PCMSK2 _SFR_MEM8(0x6D) |

| #define | PCMSK2_struct _SFR_MEM8_STRUCT(0x6d, struct __reg_PCMSK2) |

| #define | PCINT16 0 |

| #define | PCINT17 1 |

| #define | PCINT18 2 |

| #define | PCINT19 3 |

| #define | PCINT20 4 |

| #define | PCINT21 5 |

| #define | PCINT22 6 |

| #define | PCINT23 7 |

| #define | TIMSK0 _SFR_MEM8(0x6E) |

| #define | TIMSK0_struct _SFR_MEM8_STRUCT(0x6e, struct __reg_TIMSK0) |

| #define | TOIE0 0 |

| #define | OCIE0A 1 |

| #define | OCIE0B 2 |

| #define | TIMSK1 _SFR_MEM8(0x6F) |

| #define | TIMSK1_struct _SFR_MEM8_STRUCT(0x6f, struct __reg_TIMSK1) |

| #define | TOIE1 0 |

| #define | OCIE1A 1 |

| #define | OCIE1B 2 |

| #define | OCIE1C 3 |

| #define | ICIE1 5 |

| #define | TIMSK2 _SFR_MEM8(0x70) |

| #define | TIMSK2_struct _SFR_MEM8_STRUCT(0x70, struct __reg_TIMSK2) |

| #define | TOIE2 0 |

| #define | TOIE2A 0 |

| #define | OCIE2A 1 |

| #define | OCIE2B 2 |

| #define | TIMSK3 _SFR_MEM8(0x71) |

| #define | TIMSK3_struct _SFR_MEM8_STRUCT(0x71, struct __reg_TIMSK3) |

| #define | TOIE3 0 |

| #define | OCIE3A 1 |

| #define | OCIE3B 2 |

| #define | OCIE3C 3 |

| #define | ICIE3 5 |

| #define | TIMSK4 _SFR_MEM8(0x72) |

| #define | TIMSK4_struct _SFR_MEM8_STRUCT(0x72, struct __reg_TIMSK4) |

| #define | TOIE4 0 |

| #define | OCIE4A 1 |

| #define | OCIE4B 2 |

| #define | OCIE4C 3 |

| #define | ICIE4 5 |

| #define | TIMSK5 _SFR_MEM8(0x73) |

| #define | TIMSK5_struct _SFR_MEM8_STRUCT(0x73, struct __reg_TIMSK5) |

| #define | TOIE5 0 |

| #define | OCIE5A 1 |

| #define | OCIE5B 2 |

| #define | OCIE5C 3 |

| #define | ICIE5 5 |

| #define | NEMCR _SFR_MEM8(0x75) |

| #define | NEMCR_struct _SFR_MEM8_STRUCT(0x75, struct __reg_NEMCR) |

| #define | AEAM0 4 |

| #define | AEAM1 5 |

| #define | ENEAM 6 |

| #define | ADCSRC _SFR_MEM8(0x77) |

| #define | ADCSRC_struct _SFR_MEM8_STRUCT(0x77, struct __reg_ADCSRC) |

| #define | ADSUT0 0 |

| #define | ADSUT1 1 |

| #define | ADSUT2 2 |

| #define | ADSUT3 3 |

| #define | ADSUT4 4 |

| #define | ADTHT0 6 |

| #define | ADTHT1 7 |

| #define | ADC _SFR_MEM16(0x78) |

| #define | ADCL _SFR_MEM8(0x78) |

| #define | ADCH _SFR_MEM8(0x79) |

| #define | ADCW _SFR_MEM16(0x78) |

| #define | ADCWL _SFR_MEM8(0x78) |

| #define | ADCWH _SFR_MEM8(0x79) |

| #define | ADCSRA _SFR_MEM8(0x7A) |

| #define | ADCSRA_struct _SFR_MEM8_STRUCT(0x7a, struct __reg_ADCSRA) |

| #define | ADPS0 0 |

| #define | ADPS1 1 |

| #define | ADPS2 2 |

| #define | ADIE 3 |

| #define | ADIF 4 |

| #define | ADATE 5 |

| #define | ADSC 6 |

| #define | ADEN 7 |

| #define | ADCSRB _SFR_MEM8(0x7B) |

| #define | ADCSRB_struct _SFR_MEM8_STRUCT(0x7b, struct __reg_ADCSRB) |

| #define | ADTS0 0 |

| #define | ADTS1 1 |

| #define | ADTS2 2 |

| #define | MUX5 3 |

| #define | ACCH 4 |

| #define | REFOK 5 |

| #define | ACME 6 |

| #define | AVDDOK 7 |

| #define | ADMUX _SFR_MEM8(0x7C) |

| #define | ADMUX_struct _SFR_MEM8_STRUCT(0x7c, struct __reg_ADMUX) |

| #define | MUX0 0 |

| #define | MUX1 1 |

| #define | MUX2 2 |

| #define | MUX3 3 |

| #define | MUX4 4 |

| #define | ADLAR 5 |

| #define | REFS0 6 |

| #define | REFS1 7 |

| #define | DIDR2 _SFR_MEM8(0x7D) |

| #define | DIDR2_struct _SFR_MEM8_STRUCT(0x7d, struct __reg_DIDR2) |

| #define | ADC8D 0 |

| #define | ADC9D 1 |

| #define | ADC10D 2 |

| #define | ADC11D 3 |

| #define | ADC12D 4 |

| #define | ADC13D 5 |

| #define | ADC14D 6 |

| #define | ADC15D 7 |

| #define | DIDR0 _SFR_MEM8(0x7E) |

| #define | DIDR0_struct _SFR_MEM8_STRUCT(0x7e, struct __reg_DIDR0) |

| #define | ADC0D 0 |

| #define | ADC1D 1 |

| #define | ADC2D 2 |

| #define | ADC3D 3 |

| #define | ADC4D 4 |

| #define | ADC5D 5 |

| #define | ADC6D 6 |

| #define | ADC7D 7 |

| #define | DIDR1 _SFR_MEM8(0x7F) |

| #define | DIDR1_struct _SFR_MEM8_STRUCT(0x7f, struct __reg_DIDR1) |

| #define | AIN0D 0 |

| #define | AIN1D 1 |

| #define | TCCR1A _SFR_MEM8(0x80) |

| #define | TCCR1A_struct _SFR_MEM8_STRUCT(0x80, struct __reg_TCCR1A) |

| #define | WGM10 0 |

| #define | WGM11 1 |

| #define | COM1C0 2 |

| #define | COM1C1 3 |

| #define | COM1B0 4 |

| #define | COM1B1 5 |

| #define | COM1A0 6 |

| #define | COM1A1 7 |

| #define | TCCR1B _SFR_MEM8(0x81) |

| #define | TCCR1B_struct _SFR_MEM8_STRUCT(0x81, struct __reg_TCCR1B) |

| #define | CS10 0 |

| #define | CS11 1 |

| #define | CS12 2 |

| #define | WGM12 3 |

| #define | WGM13 4 |

| #define | ICES1 6 |

| #define | ICNC1 7 |

| #define | TCCR1C _SFR_MEM8(0x82) |

| #define | TCCR1C_struct _SFR_MEM8_STRUCT(0x82, struct __reg_TCCR1C) |

| #define | FOC1C 5 |

| #define | FOC1B 6 |

| #define | FOC1A 7 |

| #define | TCNT1 _SFR_MEM16(0x84) |

| #define | TCNT1L _SFR_MEM8(0x84) |

| #define | TCNT1H _SFR_MEM8(0x85) |

| #define | ICR1 _SFR_MEM16(0x86) |

| #define | ICR1L _SFR_MEM8(0x86) |

| #define | ICR1H _SFR_MEM8(0x87) |

| #define | OCR1A _SFR_MEM16(0x88) |

| #define | OCR1AL _SFR_MEM8(0x88) |

| #define | OCR1AH _SFR_MEM8(0x89) |

| #define | OCR1B _SFR_MEM16(0x8A) |

| #define | OCR1BL _SFR_MEM8(0x8A) |

| #define | OCR1BH _SFR_MEM8(0x8B) |

| #define | OCR1C _SFR_MEM16(0x8C) |

| #define | OCR1CL _SFR_MEM8(0x8C) |

| #define | OCR1CH _SFR_MEM8(0x8D) |

| #define | TCCR3A _SFR_MEM8(0x90) |

| #define | TCCR3A_struct _SFR_MEM8_STRUCT(0x90, struct __reg_TCCR3A) |

| #define | WGM30 0 |

| #define | WGM31 1 |

| #define | COM3C0 2 |

| #define | COM3C1 3 |

| #define | COM3B0 4 |

| #define | COM3B1 5 |

| #define | COM3A0 6 |

| #define | COM3A1 7 |

| #define | TCCR3B _SFR_MEM8(0x91) |

| #define | TCCR3B_struct _SFR_MEM8_STRUCT(0x91, struct __reg_TCCR3B) |

| #define | CS30 0 |

| #define | CS31 1 |

| #define | CS32 2 |

| #define | WGM32 3 |

| #define | WGM33 4 |

| #define | ICES3 6 |

| #define | ICNC3 7 |

| #define | TCCR3C _SFR_MEM8(0x92) |

| #define | TCCR3C_struct _SFR_MEM8_STRUCT(0x92, struct __reg_TCCR3C) |

| #define | FOC3C 5 |

| #define | FOC3B 6 |

| #define | FOC3A 7 |

| #define | TCNT3 _SFR_MEM16(0x94) |

| #define | TCNT3L _SFR_MEM8(0x94) |

| #define | TCNT3H _SFR_MEM8(0x95) |

| #define | ICR3 _SFR_MEM16(0x96) |

| #define | ICR3L _SFR_MEM8(0x96) |

| #define | ICR3H _SFR_MEM8(0x97) |

| #define | OCR3A _SFR_MEM16(0x98) |

| #define | OCR3AL _SFR_MEM8(0x98) |

| #define | OCR3AH _SFR_MEM8(0x99) |

| #define | OCR3B _SFR_MEM16(0x9A) |

| #define | OCR3BL _SFR_MEM8(0x9A) |

| #define | OCR3BH _SFR_MEM8(0x9B) |

| #define | OCR3C _SFR_MEM16(0x9C) |

| #define | OCR3CL _SFR_MEM8(0x9C) |

| #define | OCR3CH _SFR_MEM8(0x9D) |

| #define | TCCR4A _SFR_MEM8(0xA0) |

| #define | TCCR4A_struct _SFR_MEM8_STRUCT(0xa0, struct __reg_TCCR4A) |

| #define | WGM40 0 |

| #define | WGM41 1 |

| #define | COM4C0 2 |

| #define | COM4C1 3 |

| #define | COM4B0 4 |

| #define | COM4B1 5 |

| #define | COM4A0 6 |

| #define | COM4A1 7 |

| #define | TCCR4B _SFR_MEM8(0xA1) |

| #define | TCCR4B_struct _SFR_MEM8_STRUCT(0xa1, struct __reg_TCCR4B) |

| #define | CS40 0 |

| #define | CS41 1 |

| #define | CS42 2 |

| #define | WGM42 3 |

| #define | WGM43 4 |

| #define | ICES4 6 |

| #define | ICNC4 7 |

| #define | TCCR4C _SFR_MEM8(0xA2) |

| #define | TCCR4C_struct _SFR_MEM8_STRUCT(0xa2, struct __reg_TCCR4C) |

| #define | FOC4C 5 |

| #define | FOC4B 6 |

| #define | FOC4A 7 |

| #define | TCNT4 _SFR_MEM16(0xA4) |

| #define | TCNT4L _SFR_MEM8(0xA4) |

| #define | TCNT4H _SFR_MEM8(0xA5) |

| #define | ICR4 _SFR_MEM16(0xA6) |

| #define | ICR4L _SFR_MEM8(0xA6) |

| #define | ICR4H _SFR_MEM8(0xA7) |

| #define | OCR4A _SFR_MEM16(0xA8) |

| #define | OCR4AL _SFR_MEM8(0xA8) |

| #define | OCR4AH _SFR_MEM8(0xA9) |

| #define | OCR4B _SFR_MEM16(0xAA) |

| #define | OCR4BL _SFR_MEM8(0xAA) |

| #define | OCR4BH _SFR_MEM8(0xAB) |

| #define | OCR4C _SFR_MEM16(0xAC) |

| #define | OCR4CL _SFR_MEM8(0xAC) |

| #define | OCR4CH _SFR_MEM8(0xAD) |

| #define | TCCR2A _SFR_MEM8(0xB0) |

| #define | TCCR2A_struct _SFR_MEM8_STRUCT(0xb0, struct __reg_TCCR2A) |

| #define | WGM20 0 |

| #define | WGM21 1 |

| #define | COM2B0 4 |

| #define | COM2B1 5 |

| #define | COM2A0 6 |

| #define | COM2A1 7 |

| #define | TCCR2B _SFR_MEM8(0xB1) |

| #define | TCCR2B_struct _SFR_MEM8_STRUCT(0xb1, struct __reg_TCCR2B) |

| #define | CS20 0 |

| #define | CS21 1 |

| #define | CS22 2 |

| #define | WGM22 3 |

| #define | FOC2B 6 |

| #define | FOC2A 7 |

| #define | TCNT2 _SFR_MEM8(0xB2) |

| #define | TCNT20 0 |

| #define | TCNT21 1 |

| #define | TCNT22 2 |

| #define | TCNT23 3 |

| #define | TCNT24 4 |

| #define | TCNT25 5 |

| #define | TCNT26 6 |

| #define | TCNT27 7 |

| #define | OCR2A _SFR_MEM8(0xB3) |

| #define | OCR2A0 0 |

| #define | OCR2A1 1 |

| #define | OCR2A2 2 |

| #define | OCR2A3 3 |

| #define | OCR2A4 4 |

| #define | OCR2A5 5 |

| #define | OCR2A6 6 |

| #define | OCR2A7 7 |

| #define | OCR2B _SFR_MEM8(0xB4) |

| #define | OCR2B0 0 |

| #define | OCR2B1 1 |

| #define | OCR2B2 2 |

| #define | OCR2B3 3 |

| #define | OCR2B4 4 |

| #define | OCR2B5 5 |

| #define | OCR2B6 6 |

| #define | OCR2B7 7 |

| #define | ASSR _SFR_MEM8(0xB6) |

| #define | ASSR_struct _SFR_MEM8_STRUCT(0xb6, struct __reg_ASSR) |

| #define | TCR2BUB 0 |

| #define | TCR2AUB 1 |

| #define | OCR2BUB 2 |

| #define | OCR2AUB 3 |

| #define | TCN2UB 4 |

| #define | AS2 5 |

| #define | EXCLK 6 |

| #define | EXCLKAMR 7 |

| #define | TWBR _SFR_MEM8(0xB8) |

| #define | TWBR0 0 |

| #define | TWBR1 1 |

| #define | TWBR2 2 |

| #define | TWBR3 3 |

| #define | TWBR4 4 |

| #define | TWBR5 5 |

| #define | TWBR6 6 |

| #define | TWBR7 7 |

| #define | TWSR _SFR_MEM8(0xB9) |

| #define | TWSR_struct _SFR_MEM8_STRUCT(0xb9, struct __reg_TWSR) |

| #define | TWPS0 0 |

| #define | TWPS1 1 |

| #define | TWS3 3 |

| #define | TWS4 4 |

| #define | TWS5 5 |

| #define | TWS6 6 |

| #define | TWS7 7 |

| #define | TWAR _SFR_MEM8(0xBA) |

| #define | TWAR_struct _SFR_MEM8_STRUCT(0xba, struct __reg_TWAR) |

| #define | TWGCE 0 |

| #define | TWA0 1 |

| #define | TWA1 2 |

| #define | TWA2 3 |

| #define | TWA3 4 |

| #define | TWA4 5 |

| #define | TWA5 6 |

| #define | TWA6 7 |

| #define | TWDR _SFR_MEM8(0xBB) |

| #define | TWD0 0 |

| #define | TWD1 1 |

| #define | TWD2 2 |

| #define | TWD3 3 |

| #define | TWD4 4 |

| #define | TWD5 5 |

| #define | TWD6 6 |

| #define | TWD7 7 |

| #define | TWCR _SFR_MEM8(0xBC) |

| #define | TWCR_struct _SFR_MEM8_STRUCT(0xbc, struct __reg_TWCR) |

| #define | TWIE 0 |

| #define | TWEN 2 |

| #define | TWWC 3 |

| #define | TWSTO 4 |

| #define | TWSTA 5 |

| #define | TWEA 6 |

| #define | TWINT 7 |

| #define | TWAMR _SFR_MEM8(0xBD) |

| #define | TWAMR_struct _SFR_MEM8_STRUCT(0xbd, struct __reg_TWAMR) |

| #define | TWAM0 1 |

| #define | TWAMR0 1 |

| #define | TWAM1 2 |

| #define | TWAMR1 2 |

| #define | TWAM2 3 |

| #define | TWAMR2 3 |

| #define | TWAM3 4 |

| #define | TWAMR3 4 |

| #define | TWAM4 5 |

| #define | TWAMR4 5 |

| #define | TWAM5 6 |

| #define | TWAMR5 6 |

| #define | TWAM6 7 |

| #define | TWAMR6 7 |

| #define | UCSR0A _SFR_MEM8(0xC0) |

| #define | UCSR0A_struct _SFR_MEM8_STRUCT(0xc0, struct __reg_UCSR0A) |

| #define | MPCM0 0 |

| #define | U2X0 1 |

| #define | UPE0 2 |

| #define | DOR0 3 |

| #define | FE0 4 |

| #define | UDRE0 5 |

| #define | TXC0 6 |

| #define | RXC0 7 |

| #define | UCSR0B _SFR_MEM8(0xC1) |

| #define | UCSR0B_struct _SFR_MEM8_STRUCT(0xc1, struct __reg_UCSR0B) |

| #define | TXB80 0 |

| #define | RXB80 1 |

| #define | UCSZ02 2 |

| #define | TXEN0 3 |

| #define | RXEN0 4 |

| #define | UDRIE0 5 |

| #define | TXCIE0 6 |

| #define | RXCIE0 7 |

| #define | UCSR0C _SFR_MEM8(0xC2) |

| #define | UCSR0C_struct _SFR_MEM8_STRUCT(0xc2, struct __reg_UCSR0C) |

| #define | UCPOL0 0 |

| #define | UCPHA0 1 |

| #define | UCPHA0 1 |

| #define | UCSZ00 1 |

| #define | UDORD0 2 |

| #define | UDORD0 2 |

| #define | UCSZ01 2 |

| #define | USBS0 3 |

| #define | UPM00 4 |

| #define | UPM01 5 |

| #define | UMSEL00 6 |

| #define | UMSEL0 6 |

| #define | UMSEL01 7 |

| #define | UMSEL1 7 |

| #define | UBRR0 _SFR_MEM16(0xC4) |

| #define | UBRR0L _SFR_MEM8(0xC4) |

| #define | UBRR0H _SFR_MEM8(0xC5) |

| #define | UDR0 _SFR_MEM8(0xC6) |

| #define | UDR00 0 |

| #define | UDR01 1 |

| #define | UDR02 2 |

| #define | UDR03 3 |

| #define | UDR04 4 |

| #define | UDR05 5 |

| #define | UDR06 6 |

| #define | UDR07 7 |

| #define | UCSR1A _SFR_MEM8(0xC8) |

| #define | UCSR1A_struct _SFR_MEM8_STRUCT(0xc8, struct __reg_UCSR1A) |

| #define | MPCM1 0 |

| #define | U2X1 1 |

| #define | UPE1 2 |

| #define | DOR1 3 |

| #define | FE1 4 |

| #define | UDRE1 5 |

| #define | TXC1 6 |

| #define | RXC1 7 |

| #define | UCSR1B _SFR_MEM8(0xC9) |

| #define | UCSR1B_struct _SFR_MEM8_STRUCT(0xc9, struct __reg_UCSR1B) |

| #define | TXB81 0 |

| #define | RXB81 1 |

| #define | UCSZ12 2 |

| #define | TXEN1 3 |

| #define | RXEN1 4 |

| #define | UDRIE1 5 |

| #define | TXCIE1 6 |

| #define | RXCIE1 7 |

| #define | UCSR1C _SFR_MEM8(0xCA) |

| #define | UCSR1C_struct _SFR_MEM8_STRUCT(0xca, struct __reg_UCSR1C) |

| #define | UCPOL1 0 |

| #define | UCPHA1 1 |

| #define | UCPHA1 1 |

| #define | UCSZ10 1 |

| #define | UDORD1 2 |

| #define | UDORD1 2 |

| #define | UCSZ11 2 |

| #define | USBS1 3 |

| #define | UPM10 4 |

| #define | UPM11 5 |

| #define | UMSEL10 6 |

| #define | UMSEL11 7 |

| #define | UBRR1 _SFR_MEM16(0xCC) |

| #define | UBRR1L _SFR_MEM8(0xCC) |

| #define | UBRR1H _SFR_MEM8(0xCD) |

| #define | UDR1 _SFR_MEM8(0xCE) |

| #define | UDR10 0 |

| #define | UDR11 1 |

| #define | UDR12 2 |

| #define | UDR13 3 |

| #define | UDR14 4 |

| #define | UDR15 5 |

| #define | UDR16 6 |

| #define | UDR17 7 |

| #define | SCCR0 _SFR_MEM8(0xDC) |

| #define | SCCR0_struct _SFR_MEM8_STRUCT(0xdc, struct __reg_SCCR0) |

| #define | SCCMP1 0 |

| #define | SCCMP2 1 |

| #define | SCCMP3 2 |

| #define | SCTSE 3 |

| #define | SCCKSEL 4 |

| #define | SCEN 5 |

| #define | SCMBTS 6 |

| #define | SCRES 7 |

| #define | SCCR1 _SFR_MEM8(0xDD) |

| #define | SCCR1_struct _SFR_MEM8_STRUCT(0xdd, struct __reg_SCCR1) |

| #define | SCENBO 0 |

| #define | SCSR _SFR_MEM8(0xDE) |

| #define | SCSR_struct _SFR_MEM8_STRUCT(0xde, struct __reg_SCSR) |

| #define | SCBSY 0 |

| #define | SCIRQM _SFR_MEM8(0xDF) |

| #define | SCIRQM_struct _SFR_MEM8_STRUCT(0xdf, struct __reg_SCIRQM) |

| #define | IRQMCP1 0 |

| #define | IRQMCP2 1 |

| #define | IRQMCP3 2 |

| #define | IRQMOF 3 |

| #define | IRQMBO 4 |

| #define | SCIRQS _SFR_MEM8(0xE0) |

| #define | SCIRQS_struct _SFR_MEM8_STRUCT(0xe0, struct __reg_SCIRQS) |

| #define | IRQSCP1 0 |

| #define | IRQSCP2 1 |

| #define | IRQSCP3 2 |

| #define | IRQSOF 3 |

| #define | IRQSBO 4 |

| #define | SCCNTLL _SFR_MEM8(0xE1) |

| #define | SCCNTLL_struct _SFR_MEM8_STRUCT(0xe1, struct __reg_SCCNTLL) |

| #define | SCCNTLL0 0 |

| #define | SCCNTLL1 1 |

| #define | SCCNTLL2 2 |

| #define | SCCNTLL3 3 |

| #define | SCCNTLL4 4 |

| #define | SCCNTLL5 5 |

| #define | SCCNTLL6 6 |

| #define | SCCNTLL7 7 |

| #define | SCCNTLH _SFR_MEM8(0xE2) |

| #define | SCCNTLH_struct _SFR_MEM8_STRUCT(0xe2, struct __reg_SCCNTLH) |

| #define | SCCNTLH0 0 |

| #define | SCCNTLH1 1 |

| #define | SCCNTLH2 2 |

| #define | SCCNTLH3 3 |

| #define | SCCNTLH4 4 |

| #define | SCCNTLH5 5 |

| #define | SCCNTLH6 6 |

| #define | SCCNTLH7 7 |

| #define | SCCNTHL _SFR_MEM8(0xE3) |

| #define | SCCNTHL_struct _SFR_MEM8_STRUCT(0xe3, struct __reg_SCCNTHL) |

| #define | SCCNTHL0 0 |

| #define | SCCNTHL1 1 |

| #define | SCCNTHL2 2 |

| #define | SCCNTHL3 3 |

| #define | SCCNTHL4 4 |

| #define | SCCNTHL5 5 |

| #define | SCCNTHL6 6 |

| #define | SCCNTHL7 7 |

| #define | SCCNTHH _SFR_MEM8(0xE4) |

| #define | SCCNTHH_struct _SFR_MEM8_STRUCT(0xe4, struct __reg_SCCNTHH) |

| #define | SCCNTHH0 0 |

| #define | SCCNTHH1 1 |

| #define | SCCNTHH2 2 |

| #define | SCCNTHH3 3 |

| #define | SCCNTHH4 4 |

| #define | SCCNTHH5 5 |

| #define | SCCNTHH6 6 |

| #define | SCCNTHH7 7 |

| #define | SCBTSRLL _SFR_MEM8(0xE5) |

| #define | SCBTSRLL_struct _SFR_MEM8_STRUCT(0xe5, struct __reg_SCBTSRLL) |

| #define | SCBTSRLL0 0 |

| #define | SCBTSRLL1 1 |

| #define | SCBTSRLL2 2 |

| #define | SCBTSRLL3 3 |

| #define | SCBTSRLL4 4 |

| #define | SCBTSRLL5 5 |

| #define | SCBTSRLL6 6 |

| #define | SCBTSRLL7 7 |

| #define | SCBTSRLH _SFR_MEM8(0xE6) |

| #define | SCBTSRLH_struct _SFR_MEM8_STRUCT(0xe6, struct __reg_SCBTSRLH) |

| #define | SCBTSRLH0 0 |

| #define | SCBTSRLH1 1 |

| #define | SCBTSRLH2 2 |

| #define | SCBTSRLH3 3 |

| #define | SCBTSRLH4 4 |

| #define | SCBTSRLH5 5 |

| #define | SCBTSRLH6 6 |

| #define | SCBTSRLH7 7 |

| #define | SCBTSRHL _SFR_MEM8(0xE7) |

| #define | SCBTSRHL_struct _SFR_MEM8_STRUCT(0xe7, struct __reg_SCBTSRHL) |

| #define | SCBTSRHL0 0 |

| #define | SCBTSRHL1 1 |

| #define | SCBTSRHL2 2 |

| #define | SCBTSRHL3 3 |

| #define | SCBTSRHL4 4 |

| #define | SCBTSRHL5 5 |

| #define | SCBTSRHL6 6 |

| #define | SCBTSRHL7 7 |

| #define | SCBTSRHH _SFR_MEM8(0xE8) |

| #define | SCBTSRHH_struct _SFR_MEM8_STRUCT(0xe8, struct __reg_SCBTSRHH) |

| #define | SCBTSRHH0 0 |

| #define | SCBTSRHH1 1 |

| #define | SCBTSRHH2 2 |

| #define | SCBTSRHH3 3 |

| #define | SCBTSRHH4 4 |

| #define | SCBTSRHH5 5 |

| #define | SCBTSRHH6 6 |

| #define | SCBTSRHH7 7 |

| #define | SCTSRLL _SFR_MEM8(0xE9) |

| #define | SCTSRLL_struct _SFR_MEM8_STRUCT(0xe9, struct __reg_SCTSRLL) |

| #define | SCTSRLL0 0 |

| #define | SCTSRLL1 1 |

| #define | SCTSRLL2 2 |

| #define | SCTSRLL3 3 |

| #define | SCTSRLL4 4 |

| #define | SCTSRLL5 5 |

| #define | SCTSRLL6 6 |

| #define | SCTSRLL7 7 |

| #define | SCTSRLH _SFR_MEM8(0xEA) |

| #define | SCTSRLH_struct _SFR_MEM8_STRUCT(0xea, struct __reg_SCTSRLH) |

| #define | SCTSRLH0 0 |

| #define | SCTSRLH1 1 |

| #define | SCTSRLH2 2 |

| #define | SCTSRLH3 3 |

| #define | SCTSRLH4 4 |

| #define | SCTSRLH5 5 |

| #define | SCTSRLH6 6 |

| #define | SCTSRLH7 7 |

| #define | SCTSRHL _SFR_MEM8(0xEB) |

| #define | SCTSRHL_struct _SFR_MEM8_STRUCT(0xeb, struct __reg_SCTSRHL) |

| #define | SCTSRHL0 0 |

| #define | SCTSRHL1 1 |

| #define | SCTSRHL2 2 |

| #define | SCTSRHL3 3 |

| #define | SCTSRHL4 4 |

| #define | SCTSRHL5 5 |

| #define | SCTSRHL6 6 |

| #define | SCTSRHL7 7 |

| #define | SCTSRHH _SFR_MEM8(0xEC) |

| #define | SCTSRHH_struct _SFR_MEM8_STRUCT(0xec, struct __reg_SCTSRHH) |

| #define | SCTSRHH0 0 |

| #define | SCTSRHH1 1 |

| #define | SCTSRHH2 2 |

| #define | SCTSRHH3 3 |

| #define | SCTSRHH4 4 |

| #define | SCTSRHH5 5 |

| #define | SCTSRHH6 6 |

| #define | SCTSRHH7 7 |

| #define | SCOCR3LL _SFR_MEM8(0xED) |

| #define | SCOCR3LL_struct _SFR_MEM8_STRUCT(0xed, struct __reg_SCOCR3LL) |

| #define | SCOCR3LL0 0 |

| #define | SCOCR3LL1 1 |

| #define | SCOCR3LL2 2 |

| #define | SCOCR3LL3 3 |

| #define | SCOCR3LL4 4 |

| #define | SCOCR3LL5 5 |

| #define | SCOCR3LL6 6 |

| #define | SCOCR3LL7 7 |

| #define | SCOCR3LH _SFR_MEM8(0xEE) |

| #define | SCOCR3LH_struct _SFR_MEM8_STRUCT(0xee, struct __reg_SCOCR3LH) |

| #define | SCOCR3LH0 0 |

| #define | SCOCR3LH1 1 |

| #define | SCOCR3LH2 2 |

| #define | SCOCR3LH3 3 |

| #define | SCOCR3LH4 4 |

| #define | SCOCR3LH5 5 |

| #define | SCOCR3LH6 6 |

| #define | SCOCR3LH7 7 |

| #define | SCOCR3HL _SFR_MEM8(0xEF) |

| #define | SCOCR3HL_struct _SFR_MEM8_STRUCT(0xef, struct __reg_SCOCR3HL) |

| #define | SCOCR3HL0 0 |

| #define | SCOCR3HL1 1 |

| #define | SCOCR3HL2 2 |

| #define | SCOCR3HL3 3 |

| #define | SCOCR3HL4 4 |

| #define | SCOCR3HL5 5 |

| #define | SCOCR3HL6 6 |

| #define | SCOCR3HL7 7 |

| #define | SCOCR3HH _SFR_MEM8(0xF0) |

| #define | SCOCR3HH_struct _SFR_MEM8_STRUCT(0xf0, struct __reg_SCOCR3HH) |

| #define | SCOCR3HH0 0 |

| #define | SCOCR3HH1 1 |

| #define | SCOCR3HH2 2 |

| #define | SCOCR3HH3 3 |

| #define | SCOCR3HH4 4 |

| #define | SCOCR3HH5 5 |

| #define | SCOCR3HH6 6 |

| #define | SCOCR3HH7 7 |

| #define | SCOCR2LL _SFR_MEM8(0xF1) |

| #define | SCOCR2LL_struct _SFR_MEM8_STRUCT(0xf1, struct __reg_SCOCR2LL) |

| #define | SCOCR2LL0 0 |

| #define | SCOCR2LL1 1 |

| #define | SCOCR2LL2 2 |

| #define | SCOCR2LL3 3 |

| #define | SCOCR2LL4 4 |

| #define | SCOCR2LL5 5 |

| #define | SCOCR2LL6 6 |

| #define | SCOCR2LL7 7 |

| #define | SCOCR2LH _SFR_MEM8(0xF2) |

| #define | SCOCR2LH_struct _SFR_MEM8_STRUCT(0xf2, struct __reg_SCOCR2LH) |

| #define | SCOCR2LH0 0 |

| #define | SCOCR2LH1 1 |

| #define | SCOCR2LH2 2 |

| #define | SCOCR2LH3 3 |

| #define | SCOCR2LH4 4 |

| #define | SCOCR2LH5 5 |

| #define | SCOCR2LH6 6 |

| #define | SCOCR2LH7 7 |

| #define | SCOCR2HL _SFR_MEM8(0xF3) |

| #define | SCOCR2HL_struct _SFR_MEM8_STRUCT(0xf3, struct __reg_SCOCR2HL) |

| #define | SCOCR2HL0 0 |

| #define | SCOCR2HL1 1 |

| #define | SCOCR2HL2 2 |

| #define | SCOCR2HL3 3 |

| #define | SCOCR2HL4 4 |

| #define | SCOCR2HL5 5 |

| #define | SCOCR2HL6 6 |

| #define | SCOCR2HL7 7 |

| #define | SCOCR2HH _SFR_MEM8(0xF4) |

| #define | SCOCR2HH_struct _SFR_MEM8_STRUCT(0xf4, struct __reg_SCOCR2HH) |

| #define | SCOCR2HH0 0 |

| #define | SCOCR2HH1 1 |

| #define | SCOCR2HH2 2 |

| #define | SCOCR2HH3 3 |

| #define | SCOCR2HH4 4 |

| #define | SCOCR2HH5 5 |

| #define | SCOCR2HH6 6 |

| #define | SCOCR2HH7 7 |

| #define | SCOCR1LL _SFR_MEM8(0xF5) |

| #define | SCOCR1LL_struct _SFR_MEM8_STRUCT(0xf5, struct __reg_SCOCR1LL) |

| #define | SCOCR1LL0 0 |

| #define | SCOCR1LL1 1 |

| #define | SCOCR1LL2 2 |

| #define | SCOCR1LL3 3 |

| #define | SCOCR1LL4 4 |

| #define | SCOCR1LL5 5 |

| #define | SCOCR1LL6 6 |

| #define | SCOCR1LL7 7 |

| #define | SCOCR1LH _SFR_MEM8(0xF6) |

| #define | SCOCR1LH_struct _SFR_MEM8_STRUCT(0xf6, struct __reg_SCOCR1LH) |

| #define | SCOCR1LH0 0 |

| #define | SCOCR1LH1 1 |

| #define | SCOCR1LH2 2 |

| #define | SCOCR1LH3 3 |

| #define | SCOCR1LH4 4 |

| #define | SCOCR1LH5 5 |

| #define | SCOCR1LH6 6 |

| #define | SCOCR1LH7 7 |

| #define | SCOCR1HL _SFR_MEM8(0xF7) |

| #define | SCOCR1HL_struct _SFR_MEM8_STRUCT(0xf7, struct __reg_SCOCR1HL) |

| #define | SCOCR1HL0 0 |

| #define | SCOCR1HL1 1 |

| #define | SCOCR1HL2 2 |

| #define | SCOCR1HL3 3 |

| #define | SCOCR1HL4 4 |

| #define | SCOCR1HL5 5 |

| #define | SCOCR1HL6 6 |

| #define | SCOCR1HL7 7 |

| #define | SCOCR1HH _SFR_MEM8(0xF8) |

| #define | SCOCR1HH_struct _SFR_MEM8_STRUCT(0xf8, struct __reg_SCOCR1HH) |

| #define | SCOCR1HH0 0 |

| #define | SCOCR1HH1 1 |

| #define | SCOCR1HH2 2 |

| #define | SCOCR1HH3 3 |

| #define | SCOCR1HH4 4 |

| #define | SCOCR1HH5 5 |

| #define | SCOCR1HH6 6 |

| #define | SCOCR1HH7 7 |

| #define | TCCR5A _SFR_MEM8(0x120) |

| #define | TCCR5A_struct _SFR_MEM8_STRUCT(0x120, struct __reg_TCCR5A) |

| #define | WGM50 0 |

| #define | WGM51 1 |

| #define | COM5C0 2 |

| #define | COM5C1 3 |

| #define | COM5B0 4 |

| #define | COM5B1 5 |

| #define | COM5A0 6 |

| #define | COM5A1 7 |

| #define | TCCR5B _SFR_MEM8(0x121) |

| #define | TCCR5B_struct _SFR_MEM8_STRUCT(0x121, struct __reg_TCCR5B) |

| #define | CS50 0 |

| #define | CS51 1 |

| #define | CS52 2 |

| #define | WGM52 3 |

| #define | WGM53 4 |

| #define | ICES5 6 |

| #define | ICNC5 7 |

| #define | TCCR5C _SFR_MEM8(0x122) |

| #define | TCCR5C_struct _SFR_MEM8_STRUCT(0x122, struct __reg_TCCR5C) |

| #define | FOC5C 5 |

| #define | FOC5B 6 |

| #define | FOC5A 7 |

| #define | TCNT5 _SFR_MEM16(0x124) |

| #define | TCNT5L _SFR_MEM8(0x124) |

| #define | TCNT5H _SFR_MEM8(0x125) |

| #define | ICR5 _SFR_MEM16(0x126) |

| #define | ICR5L _SFR_MEM8(0x126) |

| #define | ICR5H _SFR_MEM8(0x127) |

| #define | OCR5A _SFR_MEM16(0x128) |

| #define | OCR5AL _SFR_MEM8(0x128) |

| #define | OCR5AH _SFR_MEM8(0x129) |

| #define | OCR5B _SFR_MEM16(0x12A) |

| #define | OCR5BL _SFR_MEM8(0x12A) |

| #define | OCR5BH _SFR_MEM8(0x12B) |

| #define | OCR5C _SFR_MEM16(0x12C) |

| #define | OCR5CL _SFR_MEM8(0x12C) |

| #define | OCR5CH _SFR_MEM8(0x12D) |

| #define | LLCR _SFR_MEM8(0x12F) |

| #define | LLCR_struct _SFR_MEM8_STRUCT(0x12f, struct __reg_LLCR) |

| #define | LLENCAL 0 |

| #define | LLSHORT 1 |

| #define | LLTCO 2 |

| #define | LLCAL 3 |

| #define | LLCOMP 4 |

| #define | LLDONE 5 |

| #define | LLDRL _SFR_MEM8(0x130) |

| #define | LLDRL_struct _SFR_MEM8_STRUCT(0x130, struct __reg_LLDRL) |

| #define | LLDRL0 0 |

| #define | LLDRL1 1 |

| #define | LLDRL2 2 |

| #define | LLDRL3 3 |

| #define | LLDRH _SFR_MEM8(0x131) |

| #define | LLDRH_struct _SFR_MEM8_STRUCT(0x131, struct __reg_LLDRH) |

| #define | LLDRH0 0 |

| #define | LLDRH1 1 |

| #define | LLDRH2 2 |

| #define | LLDRH3 3 |

| #define | LLDRH4 4 |

| #define | DRTRAM3 _SFR_MEM8(0x132) |

| #define | DRTRAM3_struct _SFR_MEM8_STRUCT(0x132, struct __reg_DRTRAM3) |

| #define | ENDRT 4 |

| #define | DRTSWOK 5 |

| #define | DRTRAM2 _SFR_MEM8(0x133) |

| #define | DRTRAM2_struct _SFR_MEM8_STRUCT(0x133, struct __reg_DRTRAM2) |

| #define | ENDRT 4 |

| #define | DRTSWOK 5 |

| #define | DRTRAM1 _SFR_MEM8(0x134) |

| #define | DRTRAM1_struct _SFR_MEM8_STRUCT(0x134, struct __reg_DRTRAM1) |

| #define | ENDRT 4 |

| #define | DRTSWOK 5 |

| #define | DRTRAM0 _SFR_MEM8(0x135) |

| #define | DRTRAM0_struct _SFR_MEM8_STRUCT(0x135, struct __reg_DRTRAM0) |

| #define | ENDRT 4 |

| #define | DRTSWOK 5 |

| #define | DPDS0 _SFR_MEM8(0x136) |

| #define | DPDS0_struct _SFR_MEM8_STRUCT(0x136, struct __reg_DPDS0) |

| #define | PBDRV0 0 |

| #define | PBDRV1 1 |

| #define | PDDRV0 2 |

| #define | PDDRV1 3 |

| #define | PEDRV0 4 |

| #define | PEDRV1 5 |

| #define | PFDRV0 6 |

| #define | PFDRV1 7 |

| #define | DPDS1 _SFR_MEM8(0x137) |

| #define | DPDS1_struct _SFR_MEM8_STRUCT(0x137, struct __reg_DPDS1) |

| #define | PGDRV0 0 |

| #define | PGDRV1 1 |

| #define | TRXPR _SFR_MEM8(0x139) |

| #define | TRXPR_struct _SFR_MEM8_STRUCT(0x139, struct __reg_TRXPR) |

| #define | TRXRST 0 |

| #define | SLPTR 1 |

| #define | AES_CTRL _SFR_MEM8(0x13C) |

| #define | AES_CTRL_struct _SFR_MEM8_STRUCT(0x13c, struct __reg_AES_CTRL) |

| #define | AES_DIR_ENC 0 |

| #define | AES_DIR_DEC 1 |

| #define | AES_MODE_ECB 0 |

| #define | AES_MODE_CBC 1 |

| #define | AES_IM 2 |

| #define | AES_DIR 3 |

| #define | AES_MODE 5 |

| #define | AES_REQUEST 7 |

| #define | AES_STATUS _SFR_MEM8(0x13D) |

| #define | AES_STATUS_struct _SFR_MEM8_STRUCT(0x13d, struct __reg_AES_STATUS) |

| #define | AES_DONE 0 |

| #define | AES_ER 7 |

| #define | AES_STATE _SFR_MEM8(0x13E) |

| #define | AES_STATE_struct _SFR_MEM8_STRUCT(0x13e, struct __reg_AES_STATE) |

| #define | AES_STATE0 0 |

| #define | AES_STATE1 1 |

| #define | AES_STATE2 2 |

| #define | AES_STATE3 3 |

| #define | AES_STATE4 4 |

| #define | AES_STATE5 5 |

| #define | AES_STATE6 6 |

| #define | AES_STATE7 7 |

| #define | AES_KEY _SFR_MEM8(0x13F) |

| #define | AES_KEY_struct _SFR_MEM8_STRUCT(0x13f, struct __reg_AES_KEY) |

| #define | AES_KEY0 0 |

| #define | AES_KEY1 1 |

| #define | AES_KEY2 2 |

| #define | AES_KEY3 3 |

| #define | AES_KEY4 4 |

| #define | AES_KEY5 5 |

| #define | AES_KEY6 6 |

| #define | AES_KEY7 7 |

| #define | TRX_STATUS _SFR_MEM8(0x141) |

| #define | TRX_STATUS_struct _SFR_MEM8_STRUCT(0x141, struct __reg_TRX_STATUS) |

| #define | P_ON 0 |

| #define | BUSY_RX 1 |

| #define | BUSY_TX 2 |

| #define | RX_ON 6 |

| #define | TRX_OFF 8 |

| #define | PLL_ON 9 |

| #define | SLEEP 15 |

| #define | BUSY_RX_AACK 17 |

| #define | BUSY_TX_ARET 18 |

| #define | RX_AACK_ON 22 |

| #define | TX_ARET_ON 25 |

| #define | STATE_TRANSITION_IN_PROGRESS 31 |

| #define | TST_DISABLED 0 |

| #define | TST_ENABLED 1 |

| #define | CCA_BUSY 0 |

| #define | CCA_IDLE 1 |

| #define | CCA_NOT_FIN 0 |

| #define | CCA_FIN 1 |

| #define | TRX_STATUS0 0 |

| #define | TRX_STATUS1 1 |

| #define | TRX_STATUS2 2 |

| #define | TRX_STATUS3 3 |

| #define | TRX_STATUS4 4 |

| #define | TST_STATUS 5 |

| #define | CCA_STATUS 6 |

| #define | CCA_DONE 7 |

| #define | TRX_STATE _SFR_MEM8(0x142) |

| #define | TRX_STATE_struct _SFR_MEM8_STRUCT(0x142, struct __reg_TRX_STATE) |

| #define | CMD_NOP 0 |

| #define | CMD_TX_START 2 |

| #define | CMD_FORCE_TRX_OFF 3 |

| #define | CMD_FORCE_PLL_ON 4 |

| #define | CMD_RX_ON 6 |

| #define | CMD_TRX_OFF 8 |

| #define | CMD_PLL_ON 9 |

| #define | CMD_RX_AACK_ON 22 |

| #define | CMD_TX_ARET_ON 25 |

| #define | TRAC_SUCCESS 0 |

| #define | TRAC_SUCCESS_DATA_PENDING 1 |

| #define | TRAC_SUCCESS_WAIT_FOR_ACK 2 |

| #define | TRAC_CHANNEL_ACCESS_FAILURE 3 |

| #define | TRAC_NO_ACK 5 |

| #define | TRAC_INVALID 7 |

| #define | TRX_CMD0 0 |

| #define | TRX_CMD1 1 |

| #define | TRX_CMD2 2 |

| #define | TRX_CMD3 3 |

| #define | TRX_CMD4 4 |

| #define | TRAC_STATUS0 5 |

| #define | TRAC_STATUS1 6 |

| #define | TRAC_STATUS2 7 |

| #define | TRX_CTRL_0 _SFR_MEM8(0x143) |

| #define | TRX_CTRL_1 _SFR_MEM8(0x144) |

| #define | TRX_CTRL_1_struct _SFR_MEM8_STRUCT(0x144, struct __reg_TRX_CTRL_1) |

| #define | TX_AUTO_CRC_ON 5 |

| #define | IRQ_2_EXT_EN 6 |

| #define | PA_EXT_EN 7 |

| #define | PHY_TX_PWR _SFR_MEM8(0x145) |

| #define | PHY_TX_PWR_struct _SFR_MEM8_STRUCT(0x145, struct __reg_PHY_TX_PWR) |

| #define | PA_LT_2US 0 |

| #define | PA_LT_4US 1 |

| #define | PA_LT_6US 2 |

| #define | PA_LT_8US 3 |

| #define | PA_BUF_LT_0US 0 |

| #define | PA_BUF_LT_2US 1 |

| #define | PA_BUF_LT_4US 2 |

| #define | PA_BUF_LT_6US 3 |

| #define | TX_PWR0 0 |

| #define | TX_PWR1 1 |

| #define | TX_PWR2 2 |

| #define | TX_PWR3 3 |

| #define | PA_LT0 4 |

| #define | PA_LT1 5 |

| #define | PA_BUF_LT0 6 |

| #define | PA_BUF_LT1 7 |

| #define | PHY_RSSI _SFR_MEM8(0x146) |

| #define | PHY_RSSI_struct _SFR_MEM8_STRUCT(0x146, struct __reg_PHY_RSSI) |

| #define | RSSI_MIN 0 |

| #define | RSSI_MIN_PLUS_3dB 1 |

| #define | RSSI_MAX 28 |

| #define | CRC_INVALID 0 |

| #define | CRC_VALID 1 |

| #define | RSSI0 0 |

| #define | RSSI1 1 |

| #define | RSSI2 2 |

| #define | RSSI3 3 |

| #define | RSSI4 4 |

| #define | RND_VALUE0 5 |

| #define | RND_VALUE1 6 |

| #define | RX_CRC_VALID 7 |

| #define | PHY_ED_LEVEL _SFR_MEM8(0x147) |

| #define | PHY_ED_LEVEL_struct _SFR_MEM8_STRUCT(0x147, struct __reg_PHY_ED_LEVEL) |

| #define | ED_MIN 0 |

| #define | ED_MIN_PLUS_1dB 1 |

| #define | ED_MAX 84 |

| #define | ED_RESET 255 |

| #define | ED_LEVEL0 0 |

| #define | ED_LEVEL1 1 |

| #define | ED_LEVEL2 2 |

| #define | ED_LEVEL3 3 |

| #define | ED_LEVEL4 4 |

| #define | ED_LEVEL5 5 |

| #define | ED_LEVEL6 6 |

| #define | ED_LEVEL7 7 |

| #define | PHY_CC_CCA _SFR_MEM8(0x148) |

| #define | PHY_CC_CCA_struct _SFR_MEM8_STRUCT(0x148, struct __reg_PHY_CC_CCA) |

| #define | F_2405MHZ 11 |

| #define | F_2410MHZ 12 |

| #define | F_2415MHZ 13 |

| #define | F_2420MHZ 14 |

| #define | F_2425MHZ 15 |

| #define | F_2430MHZ 16 |

| #define | F_2435MHZ 17 |

| #define | F_2440MHZ 18 |

| #define | F_2445MHZ 19 |

| #define | F_2450MHZ 20 |

| #define | F_2455MHZ 21 |

| #define | F_2460MHZ 22 |

| #define | F_2465MHZ 23 |

| #define | F_2470MHZ 24 |

| #define | F_2475MHZ 25 |

| #define | F_2480MHZ 26 |

| #define | CCA_CS_OR_ED 0 |

| #define | CCA_ED 1 |

| #define | CCA_CS 2 |

| #define | CCA_CS_AND_ED 3 |

| #define | CHANNEL0 0 |

| #define | CHANNEL1 1 |

| #define | CHANNEL2 2 |

| #define | CHANNEL3 3 |

| #define | CHANNEL4 4 |

| #define | CCA_MODE0 5 |

| #define | CCA_MODE1 6 |

| #define | CCA_REQUEST 7 |

| #define | CCA_THRES _SFR_MEM8(0x149) |

| #define | CCA_THRES_struct _SFR_MEM8_STRUCT(0x149, struct __reg_CCA_THRES) |

| #define | CCA_ED_THRES0 0 |

| #define | CCA_ED_THRES1 1 |

| #define | CCA_ED_THRES2 2 |

| #define | CCA_ED_THRES3 3 |

| #define | CCA_CS_THRES0 4 |

| #define | CCA_CS_THRES1 5 |

| #define | CCA_CS_THRES2 6 |

| #define | CCA_CS_THRES3 7 |

| #define | RX_CTRL _SFR_MEM8(0x14A) |

| #define | RX_CTRL_struct _SFR_MEM8_STRUCT(0x14a, struct __reg_RX_CTRL) |

| #define | PDT_THRES_ANT_DIV_OFF 7 |

| #define | PDT_THRES_ANT_DIV_ON 3 |

| #define | PDT_THRES0 0 |

| #define | PDT_THRES1 1 |

| #define | PDT_THRES2 2 |

| #define | PDT_THRES3 3 |

| #define | SFD_VALUE _SFR_MEM8(0x14B) |

| #define | SFD_VALUE_struct _SFR_MEM8_STRUCT(0x14b, struct __reg_SFD_VALUE) |

| #define | IEEE_SFD 167 |

| #define | SFD_VALUE0 0 |

| #define | SFD_VALUE1 1 |

| #define | SFD_VALUE2 2 |

| #define | SFD_VALUE3 3 |

| #define | SFD_VALUE4 4 |

| #define | SFD_VALUE5 5 |

| #define | SFD_VALUE6 6 |

| #define | SFD_VALUE7 7 |

| #define | TRX_CTRL_2 _SFR_MEM8(0x14C) |

| #define | TRX_CTRL_2_struct _SFR_MEM8_STRUCT(0x14c, struct __reg_TRX_CTRL_2) |

| #define | RATE_250KB 0 |

| #define | RATE_500KB 1 |

| #define | RATE_1000KB 2 |

| #define | RATE_2000KB 3 |

| #define | OQPSK_DATA_RATE0 0 |

| #define | OQPSK_DATA_RATE1 1 |

| #define | RX_SAFE_MODE 7 |

| #define | ANT_DIV _SFR_MEM8(0x14D) |

| #define | ANT_DIV_struct _SFR_MEM8_STRUCT(0x14d, struct __reg_ANT_DIV) |

| #define | ANT_1 1 |

| #define | ANT_0 2 |

| #define | ANT_RESET 3 |

| #define | ANT_DIV_EXT_SW_DIS 0 |

| #define | ANT_DIV_EXT_SW_EN 1 |

| #define | ANTENNA_0 0 |

| #define | ANTENNA_1 1 |

| #define | ANT_CTRL0 0 |

| #define | ANT_CTRL1 1 |

| #define | ANT_EXT_SW_EN 2 |

| #define | ANT_DIV_EN 3 |

| #define | ANT_SEL 7 |

| #define | IRQ_MASK _SFR_MEM8(0x14E) |

| #define | IRQ_MASK_struct _SFR_MEM8_STRUCT(0x14e, struct __reg_IRQ_MASK) |

| #define | PLL_LOCK_EN 0 |

| #define | PLL_UNLOCK_EN 1 |

| #define | RX_START_EN 2 |

| #define | RX_END_EN 3 |

| #define | CCA_ED_DONE_EN 4 |

| #define | AMI_EN 5 |

| #define | TX_END_EN 6 |

| #define | AWAKE_EN 7 |

| #define | IRQ_STATUS _SFR_MEM8(0x14F) |

| #define | IRQ_STATUS_struct _SFR_MEM8_STRUCT(0x14f, struct __reg_IRQ_STATUS) |

| #define | PLL_LOCK 0 |

| #define | PLL_UNLOCK 1 |

| #define | RX_START 2 |

| #define | RX_END 3 |

| #define | CCA_ED_DONE 4 |

| #define | AMI 5 |

| #define | TX_END 6 |

| #define | AWAKE 7 |

| #define | VREG_CTRL _SFR_MEM8(0x150) |

| #define | VREG_CTRL_struct _SFR_MEM8_STRUCT(0x150, struct __reg_VREG_CTRL) |

| #define | DVDD_INT 0 |

| #define | DVDD_EXT 1 |

| #define | AVDD_INT 0 |

| #define | AVDD_EXT 1 |

| #define | DVDD_OK 2 |

| #define | DVREG_EXT 3 |

| #define | AVDD_OK 6 |

| #define | AVREG_EXT 7 |

| #define | BATMON _SFR_MEM8(0x151) |

| #define | BATMON_struct _SFR_MEM8_STRUCT(0x151, struct __reg_BATMON) |

| #define | BATMON_HR_DIS 0 |

| #define | BATMON_HR_EN 1 |

| #define | BATMON_VTH0 0 |

| #define | BATMON_VTH1 1 |

| #define | BATMON_VTH2 2 |

| #define | BATMON_VTH3 3 |

| #define | BATMON_HR 4 |

| #define | BATMON_OK 5 |

| #define | BAT_LOW_EN 6 |

| #define | BAT_LOW 7 |

| #define | XOSC_CTRL _SFR_MEM8(0x152) |

| #define | XOSC_CTRL_struct _SFR_MEM8_STRUCT(0x152, struct __reg_XOSC_CTRL) |

| #define | XTAL_TRIM_MIN 0 |

| #define | XTAL_TRIM_MAX 15 |

| #define | XTAL_TRIM0 0 |

| #define | XTAL_TRIM1 1 |

| #define | XTAL_TRIM2 2 |

| #define | XTAL_TRIM3 3 |

| #define | XTAL_MODE0 4 |

| #define | XTAL_MODE1 5 |

| #define | XTAL_MODE2 6 |

| #define | XTAL_MODE3 7 |

| #define | RX_SYN _SFR_MEM8(0x155) |

| #define | RX_SYN_struct _SFR_MEM8_STRUCT(0x155, struct __reg_RX_SYN) |

| #define | RX_PDT_LEVEL_MIN 0 |

| #define | RX_PDT_LEVEL_MAX 15 |

| #define | RX_PDT_LEVEL0 0 |

| #define | RX_PDT_LEVEL1 1 |

| #define | RX_PDT_LEVEL2 2 |

| #define | RX_PDT_LEVEL3 3 |

| #define | RX_PDT_DIS 7 |

| #define | XAH_CTRL_1 _SFR_MEM8(0x157) |

| #define | XAH_CTRL_1_struct _SFR_MEM8_STRUCT(0x157, struct __reg_XAH_CTRL_1) |

| #define | AACK_ACK_TIME_12_SYM 0 |

| #define | AACK_ACK_TIME_2_SYM 1 |

| #define | AACK_PROM_MODE 1 |

| #define | AACK_ACK_TIME 2 |

| #define | AACK_UPLD_RES_FT 4 |

| #define | AACK_FLTR_RES_FT 5 |

| #define | FTN_CTRL _SFR_MEM8(0x158) |

| #define | FTN_CTRL_struct _SFR_MEM8_STRUCT(0x158, struct __reg_FTN_CTRL) |

| #define | FTN_START 7 |

| #define | PLL_CF _SFR_MEM8(0x15A) |

| #define | PLL_CF_struct _SFR_MEM8_STRUCT(0x15a, struct __reg_PLL_CF) |

| #define | PLL_CF_START 7 |

| #define | PLL_DCU _SFR_MEM8(0x15B) |

| #define | PLL_DCU_struct _SFR_MEM8_STRUCT(0x15b, struct __reg_PLL_DCU) |

| #define | PLL_DCU_START 7 |

| #define | PART_NUM _SFR_MEM8(0x15C) |

| #define | PART_NUM_struct _SFR_MEM8_STRUCT(0x15c, struct __reg_PART_NUM) |

| #define | P_ATmega128RFA1 131 |

| #define | PART_NUM0 0 |

| #define | PART_NUM1 1 |

| #define | PART_NUM2 2 |

| #define | PART_NUM3 3 |

| #define | PART_NUM4 4 |

| #define | PART_NUM5 5 |

| #define | PART_NUM6 6 |

| #define | PART_NUM7 7 |

| #define | VERSION_NUM _SFR_MEM8(0x15D) |

| #define | VERSION_NUM_struct _SFR_MEM8_STRUCT(0x15d, struct __reg_VERSION_NUM) |

| #define | REV_A 2 |

| #define | REV_B 3 |

| #define | VERSION_NUM0 0 |

| #define | VERSION_NUM1 1 |

| #define | VERSION_NUM2 2 |

| #define | VERSION_NUM3 3 |

| #define | VERSION_NUM4 4 |

| #define | VERSION_NUM5 5 |

| #define | VERSION_NUM6 6 |

| #define | VERSION_NUM7 7 |

| #define | MAN_ID_0 _SFR_MEM8(0x15E) |

| #define | MAN_ID_0_struct _SFR_MEM8_STRUCT(0x15e, struct __reg_MAN_ID_0) |

| #define | ATMEL_BYTE_0 31 |

| #define | MAN_ID_00 0 |

| #define | MAN_ID_01 1 |

| #define | MAN_ID_02 2 |

| #define | MAN_ID_03 3 |

| #define | MAN_ID_04 4 |

| #define | MAN_ID_05 5 |

| #define | MAN_ID_06 6 |

| #define | MAN_ID_07 7 |

| #define | MAN_ID_1 _SFR_MEM8(0x15F) |

| #define | MAN_ID_1_struct _SFR_MEM8_STRUCT(0x15f, struct __reg_MAN_ID_1) |

| #define | ATMEL_BYTE_1 0 |

| #define | MAN_ID_10 0 |

| #define | MAN_ID_11 1 |

| #define | MAN_ID_12 2 |

| #define | MAN_ID_13 3 |

| #define | MAN_ID_14 4 |

| #define | MAN_ID_15 5 |

| #define | MAN_ID_16 6 |

| #define | MAN_ID_17 7 |

| #define | SHORT_ADDR_0 _SFR_MEM8(0x160) |

| #define | SHORT_ADDR_0_struct _SFR_MEM8_STRUCT(0x160, struct __reg_SHORT_ADDR_0) |

| #define | SHORT_ADDR_00 0 |

| #define | SHORT_ADDR_01 1 |

| #define | SHORT_ADDR_02 2 |

| #define | SHORT_ADDR_03 3 |

| #define | SHORT_ADDR_04 4 |

| #define | SHORT_ADDR_05 5 |

| #define | SHORT_ADDR_06 6 |

| #define | SHORT_ADDR_07 7 |

| #define | SHORT_ADDR_1 _SFR_MEM8(0x161) |

| #define | SHORT_ADDR_1_struct _SFR_MEM8_STRUCT(0x161, struct __reg_SHORT_ADDR_1) |

| #define | SHORT_ADDR_10 0 |

| #define | SHORT_ADDR_11 1 |

| #define | SHORT_ADDR_12 2 |

| #define | SHORT_ADDR_13 3 |

| #define | SHORT_ADDR_14 4 |

| #define | SHORT_ADDR_15 5 |

| #define | SHORT_ADDR_16 6 |

| #define | SHORT_ADDR_17 7 |

| #define | PAN_ID_0 _SFR_MEM8(0x162) |

| #define | PAN_ID_0_struct _SFR_MEM8_STRUCT(0x162, struct __reg_PAN_ID_0) |

| #define | PAN_ID_00 0 |

| #define | PAN_ID_01 1 |

| #define | PAN_ID_02 2 |

| #define | PAN_ID_03 3 |

| #define | PAN_ID_04 4 |

| #define | PAN_ID_05 5 |

| #define | PAN_ID_06 6 |

| #define | PAN_ID_07 7 |

| #define | PAN_ID_1 _SFR_MEM8(0x163) |

| #define | PAN_ID_1_struct _SFR_MEM8_STRUCT(0x163, struct __reg_PAN_ID_1) |

| #define | PAN_ID_10 0 |

| #define | PAN_ID_11 1 |

| #define | PAN_ID_12 2 |

| #define | PAN_ID_13 3 |

| #define | PAN_ID_14 4 |

| #define | PAN_ID_15 5 |

| #define | PAN_ID_16 6 |

| #define | PAN_ID_17 7 |

| #define | IEEE_ADDR_0 _SFR_MEM8(0x164) |

| #define | IEEE_ADDR_0_struct _SFR_MEM8_STRUCT(0x164, struct __reg_IEEE_ADDR_0) |

| #define | IEEE_ADDR_00 0 |

| #define | IEEE_ADDR_01 1 |

| #define | IEEE_ADDR_02 2 |

| #define | IEEE_ADDR_03 3 |

| #define | IEEE_ADDR_04 4 |

| #define | IEEE_ADDR_05 5 |

| #define | IEEE_ADDR_06 6 |

| #define | IEEE_ADDR_07 7 |

| #define | IEEE_ADDR_1 _SFR_MEM8(0x165) |

| #define | IEEE_ADDR_1_struct _SFR_MEM8_STRUCT(0x165, struct __reg_IEEE_ADDR_1) |

| #define | IEEE_ADDR_10 0 |

| #define | IEEE_ADDR_11 1 |

| #define | IEEE_ADDR_12 2 |

| #define | IEEE_ADDR_13 3 |

| #define | IEEE_ADDR_14 4 |

| #define | IEEE_ADDR_15 5 |

| #define | IEEE_ADDR_16 6 |

| #define | IEEE_ADDR_17 7 |

| #define | IEEE_ADDR_2 _SFR_MEM8(0x166) |

| #define | IEEE_ADDR_2_struct _SFR_MEM8_STRUCT(0x166, struct __reg_IEEE_ADDR_2) |

| #define | IEEE_ADDR_20 0 |

| #define | IEEE_ADDR_21 1 |

| #define | IEEE_ADDR_22 2 |

| #define | IEEE_ADDR_23 3 |

| #define | IEEE_ADDR_24 4 |

| #define | IEEE_ADDR_25 5 |

| #define | IEEE_ADDR_26 6 |

| #define | IEEE_ADDR_27 7 |

| #define | IEEE_ADDR_3 _SFR_MEM8(0x167) |

| #define | IEEE_ADDR_3_struct _SFR_MEM8_STRUCT(0x167, struct __reg_IEEE_ADDR_3) |

| #define | IEEE_ADDR_30 0 |

| #define | IEEE_ADDR_31 1 |

| #define | IEEE_ADDR_32 2 |

| #define | IEEE_ADDR_33 3 |

| #define | IEEE_ADDR_34 4 |

| #define | IEEE_ADDR_35 5 |

| #define | IEEE_ADDR_36 6 |

| #define | IEEE_ADDR_37 7 |

| #define | IEEE_ADDR_4 _SFR_MEM8(0x168) |

| #define | IEEE_ADDR_4_struct _SFR_MEM8_STRUCT(0x168, struct __reg_IEEE_ADDR_4) |

| #define | IEEE_ADDR_40 0 |

| #define | IEEE_ADDR_41 1 |

| #define | IEEE_ADDR_42 2 |

| #define | IEEE_ADDR_43 3 |

| #define | IEEE_ADDR_44 4 |

| #define | IEEE_ADDR_45 5 |

| #define | IEEE_ADDR_46 6 |

| #define | IEEE_ADDR_47 7 |

| #define | IEEE_ADDR_5 _SFR_MEM8(0x169) |

| #define | IEEE_ADDR_5_struct _SFR_MEM8_STRUCT(0x169, struct __reg_IEEE_ADDR_5) |

| #define | IEEE_ADDR_50 0 |

| #define | IEEE_ADDR_51 1 |

| #define | IEEE_ADDR_52 2 |

| #define | IEEE_ADDR_53 3 |

| #define | IEEE_ADDR_54 4 |

| #define | IEEE_ADDR_55 5 |

| #define | IEEE_ADDR_56 6 |

| #define | IEEE_ADDR_57 7 |

| #define | IEEE_ADDR_6 _SFR_MEM8(0x16A) |

| #define | IEEE_ADDR_6_struct _SFR_MEM8_STRUCT(0x16a, struct __reg_IEEE_ADDR_6) |

| #define | IEEE_ADDR_60 0 |

| #define | IEEE_ADDR_61 1 |

| #define | IEEE_ADDR_62 2 |

| #define | IEEE_ADDR_63 3 |

| #define | IEEE_ADDR_64 4 |

| #define | IEEE_ADDR_65 5 |

| #define | IEEE_ADDR_66 6 |

| #define | IEEE_ADDR_67 7 |

| #define | IEEE_ADDR_7 _SFR_MEM8(0x16B) |

| #define | IEEE_ADDR_7_struct _SFR_MEM8_STRUCT(0x16b, struct __reg_IEEE_ADDR_7) |

| #define | IEEE_ADDR_70 0 |

| #define | IEEE_ADDR_71 1 |

| #define | IEEE_ADDR_72 2 |

| #define | IEEE_ADDR_73 3 |

| #define | IEEE_ADDR_74 4 |

| #define | IEEE_ADDR_75 5 |

| #define | IEEE_ADDR_76 6 |

| #define | IEEE_ADDR_77 7 |

| #define | XAH_CTRL_0 _SFR_MEM8(0x16C) |

| #define | XAH_CTRL_0_struct _SFR_MEM8_STRUCT(0x16c, struct __reg_XAH_CTRL_0) |

| #define | SLOTTED_OP_DIS 0 |

| #define | SLOTTED_OP_EN 1 |

| #define | SLOTTED_OPERATION 0 |

| #define | MAX_CSMA_RETRIES0 1 |

| #define | MAX_CSMA_RETRIES1 2 |

| #define | MAX_CSMA_RETRIES2 3 |

| #define | MAX_FRAME_RETRIES0 4 |

| #define | MAX_FRAME_RETRIES1 5 |

| #define | MAX_FRAME_RETRIES2 6 |

| #define | MAX_FRAME_RETRIES3 7 |

| #define | CSMA_SEED_0 _SFR_MEM8(0x16D) |

| #define | CSMA_SEED_0_struct _SFR_MEM8_STRUCT(0x16d, struct __reg_CSMA_SEED_0) |

| #define | CSMA_SEED_00 0 |

| #define | CSMA_SEED_01 1 |

| #define | CSMA_SEED_02 2 |

| #define | CSMA_SEED_03 3 |

| #define | CSMA_SEED_04 4 |

| #define | CSMA_SEED_05 5 |

| #define | CSMA_SEED_06 6 |

| #define | CSMA_SEED_07 7 |

| #define | CSMA_SEED_1 _SFR_MEM8(0x16E) |

| #define | CSMA_SEED_1_struct _SFR_MEM8_STRUCT(0x16e, struct __reg_CSMA_SEED_1) |

| #define | CSMA_SEED_10 0 |

| #define | CSMA_SEED_11 1 |

| #define | CSMA_SEED_12 2 |

| #define | AACK_I_AM_COORD 3 |

| #define | AACK_DIS_ACK 4 |

| #define | AACK_SET_PD 5 |

| #define | AACK_FVN_MODE0 6 |

| #define | AACK_FVN_MODE1 7 |

| #define | CSMA_BE _SFR_MEM8(0x16F) |

| #define | CSMA_BE_struct _SFR_MEM8_STRUCT(0x16f, struct __reg_CSMA_BE) |

| #define | MIN_BE0 0 |

| #define | MIN_BE1 1 |

| #define | MIN_BE2 2 |

| #define | MIN_BE3 3 |

| #define | MAX_BE0 4 |

| #define | MAX_BE1 5 |

| #define | MAX_BE2 6 |

| #define | MAX_BE3 7 |

| #define | TST_CTRL_DIGI _SFR_MEM8(0x176) |

| #define | TST_CTRL_DIGI_struct _SFR_MEM8_STRUCT(0x176, struct __reg_TST_CTRL_DIGI) |

| #define | TST_CTRL_DIG0 0 |

| #define | TST_CTRL_DIG1 1 |

| #define | TST_CTRL_DIG2 2 |

| #define | TST_CTRL_DIG3 3 |

| #define | TST_RX_LENGTH _SFR_MEM8(0x17B) |

| #define | TST_RX_LENGTH_struct _SFR_MEM8_STRUCT(0x17b, struct __reg_TST_RX_LENGTH) |

| #define | RX_LENGTH0 0 |

| #define | RX_LENGTH1 1 |

| #define | RX_LENGTH2 2 |

| #define | RX_LENGTH3 3 |

| #define | RX_LENGTH4 4 |

| #define | RX_LENGTH5 5 |

| #define | RX_LENGTH6 6 |

| #define | RX_LENGTH7 7 |

| #define | TRXFBST _SFR_MEM8(0x180) |

| #define | TRXFBST0 0 |

| #define | TRXFBST1 1 |

| #define | TRXFBST2 2 |

| #define | TRXFBST3 3 |

| #define | TRXFBST4 4 |

| #define | TRXFBST5 5 |

| #define | TRXFBST6 6 |

| #define | TRXFBST7 7 |

| #define | TRXFBEND _SFR_MEM8(0x1FF) |

| #define | TRXFBEND0 0 |

| #define | TRXFBEND1 1 |

| #define | TRXFBEND2 2 |

| #define | TRXFBEND3 3 |

| #define | TRXFBEND4 4 |

| #define | TRXFBEND5 5 |

| #define | TRXFBEND6 6 |

| #define | TRXFBEND7 7 |

| #define | _VECTORS_SIZE 288 |

| #define | INT0_vect _VECTOR(1) |

| #define | INT0_vect_num 1 |

| #define | INT1_vect _VECTOR(2) |

| #define | INT1_vect_num 2 |

| #define | INT2_vect _VECTOR(3) |

| #define | INT2_vect_num 3 |

| #define | INT3_vect _VECTOR(4) |

| #define | INT3_vect_num 4 |

| #define | INT4_vect _VECTOR(5) |

| #define | INT4_vect_num 5 |

| #define | INT5_vect _VECTOR(6) |

| #define | INT5_vect_num 6 |

| #define | INT6_vect _VECTOR(7) |

| #define | INT6_vect_num 7 |

| #define | INT7_vect _VECTOR(8) |

| #define | INT7_vect_num 8 |

| #define | PCINT0_vect _VECTOR(9) |

| #define | PCINT0_vect_num 9 |

| #define | PCINT1_vect _VECTOR(10) |

| #define | PCINT1_vect_num 10 |

| #define | PCINT2_vect _VECTOR(11) |

| #define | PCINT2_vect_num 11 |

| #define | WDT_vect _VECTOR(12) |

| #define | WDT_vect_num 12 |

| #define | TIMER2_COMPA_vect _VECTOR(13) |

| #define | TIMER2_COMPA_vect_num 13 |

| #define | TIMER2_COMPB_vect _VECTOR(14) |

| #define | TIMER2_COMPB_vect_num 14 |

| #define | TIMER2_OVF_vect _VECTOR(15) |

| #define | TIMER2_OVF_vect_num 15 |

| #define | TIMER1_CAPT_vect _VECTOR(16) |

| #define | TIMER1_CAPT_vect_num 16 |

| #define | TIMER1_COMPA_vect _VECTOR(17) |

| #define | TIMER1_COMPA_vect_num 17 |

| #define | TIMER1_COMPB_vect _VECTOR(18) |

| #define | TIMER1_COMPB_vect_num 18 |

| #define | TIMER1_COMPC_vect _VECTOR(19) |

| #define | TIMER1_COMPC_vect_num 19 |

| #define | TIMER1_OVF_vect _VECTOR(20) |

| #define | TIMER1_OVF_vect_num 20 |

| #define | TIMER0_COMPA_vect _VECTOR(21) |

| #define | TIMER0_COMPA_vect_num 21 |

| #define | TIMER0_COMPB_vect _VECTOR(22) |

| #define | TIMER0_COMPB_vect_num 22 |

| #define | TIMER0_OVF_vect _VECTOR(23) |

| #define | TIMER0_OVF_vect_num 23 |

| #define | SPI_STC_vect _VECTOR(24) |

| #define | SPI_STC_vect_num 24 |

| #define | USART0_RX_vect _VECTOR(25) |

| #define | USART0_RX_vect_num 25 |

| #define | USART0_UDRE_vect _VECTOR(26) |

| #define | USART0_UDRE_vect_num 26 |

| #define | USART0_TX_vect _VECTOR(27) |

| #define | USART0_TX_vect_num 27 |

| #define | ANALOG_COMP_vect _VECTOR(28) |

| #define | ANALOG_COMP_vect_num 28 |

| #define | ADC_vect _VECTOR(29) |

| #define | ADC_vect_num 29 |

| #define | EE_READY_vect _VECTOR(30) |

| #define | EE_READY_vect_num 30 |

| #define | TIMER3_CAPT_vect _VECTOR(31) |

| #define | TIMER3_CAPT_vect_num 31 |

| #define | TIMER3_COMPA_vect _VECTOR(32) |

| #define | TIMER3_COMPA_vect_num 32 |

| #define | TIMER3_COMPB_vect _VECTOR(33) |

| #define | TIMER3_COMPB_vect_num 33 |

| #define | TIMER3_COMPC_vect _VECTOR(34) |

| #define | TIMER3_COMPC_vect_num 34 |

| #define | TIMER3_OVF_vect _VECTOR(35) |

| #define | TIMER3_OVF_vect_num 35 |

| #define | USART1_RX_vect _VECTOR(36) |

| #define | USART1_RX_vect_num 36 |

| #define | USART1_UDRE_vect _VECTOR(37) |

| #define | USART1_UDRE_vect_num 37 |

| #define | USART1_TX_vect _VECTOR(38) |

| #define | USART1_TX_vect_num 38 |

| #define | TWI_vect _VECTOR(39) |

| #define | TWI_vect_num 39 |

| #define | SPM_READY_vect _VECTOR(40) |

| #define | SPM_READY_vect_num 40 |

| #define | TIMER4_CAPT_vect _VECTOR(41) |

| #define | TIMER4_CAPT_vect_num 41 |

| #define | TIMER4_COMPA_vect _VECTOR(42) |

| #define | TIMER4_COMPA_vect_num 42 |

| #define | TIMER4_COMPB_vect _VECTOR(43) |

| #define | TIMER4_COMPB_vect_num 43 |

| #define | TIMER4_COMPC_vect _VECTOR(44) |

| #define | TIMER4_COMPC_vect_num 44 |

| #define | TIMER4_OVF_vect _VECTOR(45) |

| #define | TIMER4_OVF_vect_num 45 |

| #define | TIMER5_CAPT_vect _VECTOR(46) |

| #define | TIMER5_CAPT_vect_num 46 |

| #define | TIMER5_COMPA_vect _VECTOR(47) |

| #define | TIMER5_COMPA_vect_num 47 |

| #define | TIMER5_COMPB_vect _VECTOR(48) |

| #define | TIMER5_COMPB_vect_num 48 |

| #define | TIMER5_COMPC_vect _VECTOR(49) |

| #define | TIMER5_COMPC_vect_num 49 |

| #define | TIMER5_OVF_vect _VECTOR(50) |

| #define | TIMER5_OVF_vect_num 50 |

| #define | USART2_RX_vect _VECTOR(51) |

| #define | USART2_RX_vect_num 51 |

| #define | USART2_UDRE_vect _VECTOR(52) |

| #define | USART2_UDRE_vect_num 52 |

| #define | USART2_TX_vect _VECTOR(53) |

| #define | USART2_TX_vect_num 53 |

| #define | USART3_RX_vect _VECTOR(54) |

| #define | USART3_RX_vect_num 54 |

| #define | USART3_UDRE_vect _VECTOR(55) |

| #define | USART3_UDRE_vect_num 55 |

| #define | USART3_TX_vect _VECTOR(56) |

| #define | USART3_TX_vect_num 56 |

| #define | TRX24_PLL_LOCK_vect _VECTOR(57) |

| #define | TRX24_PLL_LOCK_vect_num 57 |

| #define | TRX24_PLL_UNLOCK_vect _VECTOR(58) |

| #define | TRX24_PLL_UNLOCK_vect_num 58 |

| #define | TRX24_RX_START_vect _VECTOR(59) |

| #define | TRX24_RX_START_vect_num 59 |

| #define | TRX24_RX_END_vect _VECTOR(60) |

| #define | TRX24_RX_END_vect_num 60 |

| #define | TRX24_CCA_ED_DONE_vect _VECTOR(61) |

| #define | TRX24_CCA_ED_DONE_vect_num 61 |

| #define | TRX24_XAH_AMI_vect _VECTOR(62) |

| #define | TRX24_XAH_AMI_vect_num 62 |

| #define | TRX24_TX_END_vect _VECTOR(63) |

| #define | TRX24_TX_END_vect_num 63 |

| #define | TRX24_AWAKE_vect _VECTOR(64) |

| #define | TRX24_AWAKE_vect_num 64 |

| #define | SCNT_CMP1_vect _VECTOR(65) |

| #define | SCNT_CMP1_vect_num 65 |

| #define | SCNT_CMP2_vect _VECTOR(66) |

| #define | SCNT_CMP2_vect_num 66 |

| #define | SCNT_CMP3_vect _VECTOR(67) |

| #define | SCNT_CMP3_vect_num 67 |

| #define | SCNT_OVFL_vect _VECTOR(68) |

| #define | SCNT_OVFL_vect_num 68 |

| #define | SCNT_BACKOFF_vect _VECTOR(69) |

| #define | SCNT_BACKOFF_vect_num 69 |

| #define | AES_READY_vect _VECTOR(70) |

| #define | AES_READY_vect_num 70 |

| #define | BAT_LOW_vect _VECTOR(71) |

| #define | BAT_LOW_vect_num 71 |

| #define | SPM_PAGESIZE (256) |

| #define | RAMSTART (0x200) |

| #define | RAMSIZE (0x4000) |

| #define | RAMEND (0x41FF) |

| #define | XRAMSTART (0x0000) |

| #define | XRAMSIZE (0x0000) |

| #define | XRAMEND RAMEND |

| #define | E2END (0xFFF) |

| #define | E2PAGESIZE (0x08) |

| #define | FLASHEND (0x1ffff) |

| #define | FUSE_MEMORY_SIZE 3 |

| #define | FUSE_CKSEL0 ~_BV(0) /* Select Clock Source */ |

| #define | FUSE_CKSEL1 ~_BV(1) /* Select Clock Source */ |

| #define | FUSE_CKSEL2 ~_BV(2) /* Select Clock Source */ |

| #define | FUSE_CKSEL3 ~_BV(3) /* Select Clock Source */ |

| #define | FUSE_SUT0 ~_BV(4) /* Select start-up time */ |

| #define | FUSE_SUT1 ~_BV(5) /* Select start-up time */ |

| #define | FUSE_CKOUT ~_BV(6) /* Clock output */ |

| #define | FUSE_CKDIV8 ~_BV(7) /* Divide clock by 8 */ |

| #define | LFUSE_DEFAULT (FUSE_CKSEL0 & FUSE_CKSEL2 & FUSE_CKSEL3 & FUSE_SUT0 & FUSE_SUT1 & FUSE_CKDIV8) |

| #define | FUSE_BOOTRST ~_BV(0) /* Select Reset Vector */ |

| #define | FUSE_BOOTSZ0 ~_BV(1) /* Select Boot Size */ |