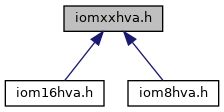

Definitions for ATmega8HVA and ATmega16HVA.

More...

Go to the source code of this file.

|

|

#define | _AVR_IOXXX_H_ "iomxxhva.h" |

| |

|

#define | PINA _SFR_IO8(0X00) |

| |

|

#define | PINA1 1 |

| |

|

#define | PINA0 0 |

| |

|

#define | DDRA _SFR_IO8(0x01) |

| |

|

#define | DDA1 1 |

| |

|

#define | DDA0 0 |

| |

|

#define | PORTA _SFR_IO8(0x02) |

| |

|

#define | PA1 1 |

| |

|

#define | PA0 0 |

| |

|

#define | PINB _SFR_IO8(0X03) |

| |

|

#define | PINB3 3 |

| |

|

#define | PINB2 2 |

| |

|

#define | PINB1 1 |

| |

|

#define | PINB0 0 |

| |

|

#define | DDRB _SFR_IO8(0x04) |

| |

|

#define | DDB3 3 |

| |

|

#define | DDB2 2 |

| |

|

#define | DDB1 1 |

| |

|

#define | DDB0 0 |

| |

|

#define | PORTB _SFR_IO8(0x05) |

| |

|

#define | PB3 3 |

| |

|

#define | PB2 2 |

| |

|

#define | PB1 1 |

| |

|

#define | PB0 0 |

| |

|

#define | PINC _SFR_IO8(0x06) |

| |

|

#define | PINC0 0 |

| |

|

#define | PORTC _SFR_IO8(0x08) |

| |

|

#define | PC0 0 |

| |

|

#define | TIFR0 _SFR_IO8(0x15) |

| |

|

#define | ICF0 3 |

| |

|

#define | OCF0B 2 |

| |

|

#define | OCF0A 1 |

| |

|

#define | TOV0 0 |

| |

|

#define | TIFR1 _SFR_IO8(0x16) |

| |

|

#define | ICF1 3 |

| |

|

#define | OCF1B 2 |

| |

|

#define | OCF1A 1 |

| |

|

#define | TOV1 0 |

| |

|

#define | OSICSR _SFR_IO8(0x17) |

| |

|

#define | OSISEL0 4 |

| |

|

#define | OSIST 1 |

| |

|

#define | OSIEN 0 |

| |

|

#define | EIFR _SFR_IO8(0x1C) |

| |

|

#define | INTF2 2 |

| |

|

#define | INTF1 1 |

| |

|

#define | INTF0 0 |

| |

|

#define | EIMSK _SFR_IO8(0x1D) |

| |

|

#define | INT2 2 |

| |

|

#define | INT1 1 |

| |

|

#define | INT0 0 |

| |

|

#define | GPIOR0 _SFR_IO8(0x1E) |

| |

|

#define | EECR _SFR_IO8(0x1F) |

| |

|

#define | EEPM1 5 |

| |

|

#define | EEPM0 4 |

| |

|

#define | EERIE 3 |

| |

|

#define | EEMPE 2 |

| |

|

#define | EEPE 1 |

| |

|

#define | EERE 0 |

| |

|

#define | EEDR _SFR_IO8(0x20) |

| |

|

#define | EEAR _SFR_IO8(0x21) |

| |

|

#define | EEARL _SFR_IO8(0x21) |

| |

|

#define | __EEPROM_REG_LOCATIONS__ 1F2021 |

| |

|

#define | GTCCR _SFR_IO8(0x23) |

| |

|

#define | TSM 7 |

| |

|

#define | PSRSYNC 0 |

| |

|

#define | TCCR0A _SFR_IO8(0x24) |

| |

|

#define | TCW0 7 |

| |

|

#define | ICEN0 6 |

| |

|

#define | ICNC0 5 |

| |

|

#define | ICES0 4 |

| |

|

#define | ICS0 3 |

| |

|

#define | WGM00 0 |

| |

|

#define | TCCR0B _SFR_IO8(0x25) |

| |

|

#define | CS02 2 |

| |

|

#define | CS01 1 |

| |

|

#define | CS00 0 |

| |

|

#define | TCNT0 _SFR_IO16(0X26) |

| |

|

#define | TCNT0L _SFR_IO8(0X26) |

| |

|

#define | TCNT0H _SFR_IO8(0X27) |

| |

|

#define | OCR0A _SFR_IO8(0x28) |

| |

|

#define | OCR0B _SFR_IO8(0X29) |

| |

|

#define | GPIOR1 _SFR_IO8(0x2A) |

| |

|

#define | GPIOR2 _SFR_IO8(0x2B) |

| |

|

#define | SPCR _SFR_IO8(0x2C) |

| |

|

#define | SPIE 7 |

| |

|

#define | SPE 6 |

| |

|

#define | DORD 5 |

| |

|

#define | MSTR 4 |

| |

|

#define | CPOL 3 |

| |

|

#define | CPHA 2 |

| |

|

#define | SPR1 1 |

| |

|

#define | SPR0 0 |

| |

|

#define | SPSR _SFR_IO8(0x2D) |

| |

|

#define | SPIF 7 |

| |

|

#define | WCOL 6 |

| |

|

#define | SPI2X 0 |

| |

|

#define | SPDR _SFR_IO8(0x2E) |

| |

|

#define | DWDR _SFR_IO8(0x31) |

| |

|

#define | IDRD 7 |

| |

|

#define | SMCR _SFR_IO8(0x33) |

| |

|

#define | SM2 3 |

| |

|

#define | SM1 2 |

| |

|

#define | SM0 1 |

| |

|

#define | SE 0 |

| |

|

#define | MCUSR _SFR_IO8(0x34) |

| |

|

#define | OCDRF 4 |

| |

|

#define | WDRF 3 |

| |

|

#define | BORF 2 |

| |

|

#define | EXTRF 1 |

| |

|

#define | PORF 0 |

| |

|

#define | MCUCR _SFR_IO8(0x35) |

| |

|

#define | CKOE 5 |

| |

|

#define | PUD 4 |

| |

|

#define | SPMCSR _SFR_IO8(0x37) |

| |

|

#define | SIGRD 5 |

| |

|

#define | CTPB 4 |

| |

|

#define | RFLB 3 |

| |

|

#define | PGWRT 2 |

| |

|

#define | PGERS 1 |

| |

|

#define | SPMEN 0 |

| |

|

#define | WDTCSR _SFR_MEM8(0x60) |

| |

|

#define | WDIF 7 |

| |

|

#define | WDIE 6 |

| |

|

#define | WDP3 5 |

| |

|

#define | WDCE 4 |

| |

|

#define | WDE 3 |

| |

|

#define | WDP2 2 |

| |

|

#define | WDP1 1 |

| |

|

#define | WDP0 0 |

| |

|

#define | CLKPR _SFR_MEM8(0x61) |

| |

|

#define | CLKPCE 7 |

| |

|

#define | CLKPS1 1 |

| |

|

#define | CLKPS0 0 |

| |

|

#define | PRR0 _SFR_MEM8(0x64) |

| |

|

#define | PRVRM 5 |

| |

|

#define | PRSPI 3 |

| |

|

#define | PRTIM1 2 |

| |

|

#define | PRTIM0 1 |

| |

|

#define | PRVADC 0 |

| |

|

#define | FOSCCAL _SFR_MEM8(0x66) |

| |

|

#define | EICRA _SFR_MEM8(0x69) |

| |

|

#define | ISC21 5 |

| |

|

#define | ISC20 4 |

| |

|

#define | ISC11 3 |

| |

|

#define | ISC10 2 |

| |

|

#define | ISC01 1 |

| |

|

#define | ISC00 0 |

| |

|

#define | TIMSK0 _SFR_MEM8(0x6E) |

| |

|

#define | ICIE0 3 |

| |

|

#define | OCIE0B 2 |

| |

|

#define | OCIE0A 1 |

| |

|

#define | TOIE0 0 |

| |

|

#define | TIMSK1 _SFR_MEM8(0x6F) |

| |

|

#define | ICIE1 3 |

| |

|

#define | OCIE1B 2 |

| |

|

#define | OCIE1A 1 |

| |

|

#define | TOIE1 0 |

| |

|

#define | VADC _SFR_MEM16(0x78) |

| |

|

#define | VADCL _SFR_MEM8(0x78) |

| |

|

#define | VADCH _SFR_MEM8(0x79) |

| |

|

#define | VADCSR _SFR_MEM8(0x7A) |

| |

|

#define | VADEN 3 |

| |

|

#define | VADSC 2 |

| |

|

#define | VADCCIF 1 |

| |

|

#define | VADCCIE 0 |

| |

|

#define | VADMUX _SFR_MEM8(0x7C) |

| |

|

#define | VADMUX3 3 |

| |

|

#define | VADMUX2 2 |

| |

|

#define | VADMUX1 1 |

| |

|

#define | VADMUX0 0 |

| |

|

#define | DIDR0 _SFR_MEM8(0x7E) |

| |

|

#define | PA1DID 1 |

| |

|

#define | PA0DID 0 |

| |

|

#define | TCCR1A _SFR_MEM8(0x80) |

| |

|

#define | TCW1 7 |

| |

|

#define | ICEN1 6 |

| |

|

#define | ICNC1 5 |

| |

|

#define | ICES1 4 |

| |

|

#define | ICS1 3 |

| |

|

#define | WGM10 0 |

| |

|

#define | TCCR1B _SFR_MEM8(0x81) |

| |

|

#define | CS12 2 |

| |

|

#define | CS11 1 |

| |

|

#define | CS10 0 |

| |

|

#define | TCNT1 _SFR_MEM16(0x84) |

| |

|

#define | TCNT1L _SFR_MEM8(0x84) |

| |

|

#define | TCNT1H _SFR_MEM8(0x85) |

| |

|

#define | OCR1A _SFR_MEM8(0x88) |

| |

|

#define | OCR1B _SFR_MEM8(0x89) |

| |

|

#define | ROCR _SFR_MEM8(0xC8) |

| |

|

#define | ROCS 7 |

| |

|

#define | ROCWIF 1 |

| |

|

#define | ROCWIE 0 |

| |

|

#define | BGCCR _SFR_MEM8(0xD0) |

| |

|

#define | BGD 7 |

| |

|

#define | BGCC5 5 |

| |

|

#define | BGCC4 4 |

| |

|

#define | BGCC3 3 |

| |

|

#define | BGCC2 2 |

| |

|

#define | BGCC1 1 |

| |

|

#define | BGCC0 0 |

| |

|

#define | BGCRR _SFR_MEM8(0xD1) |

| |

|

#define | BGCR7 7 |

| |

|

#define | BGCR6 6 |

| |

|

#define | BGCR5 5 |

| |

|

#define | BGCR4 4 |

| |

|

#define | BGCR3 3 |

| |

|

#define | BGCR2 2 |

| |

|

#define | BGCR1 1 |

| |

|

#define | BGCR0 0 |

| |

|

#define | CADAC0 _SFR_MEM8(0xE0) |

| |

|

#define | CADAC1 _SFR_MEM8(0xE1) |

| |

|

#define | CADAC2 _SFR_MEM8(0xE2) |

| |

|

#define | CADAC3 _SFR_MEM8(0xE3) |

| |

|

#define | CADCSRA _SFR_MEM8(0xE4) |

| |

|

#define | CADEN 7 |

| |

|

#define | CADPOL 6 |

| |

|

#define | CADUB 5 |

| |

|

#define | CADAS1 4 |

| |

|

#define | CADAS0 3 |

| |

|

#define | CADSI1 2 |

| |

|

#define | CADSI0 1 |

| |

|

#define | CADSE 0 |

| |

|

#define | CADCSRB _SFR_MEM8(0xE5) |

| |

|

#define | CADACIE 6 |

| |

|

#define | CADRCIE 5 |

| |

|

#define | CADICIE 4 |

| |

|

#define | CADACIF 2 |

| |

|

#define | CADRCIF 1 |

| |

|

#define | CADICIF 0 |

| |

|

#define | CADRC _SFR_MEM8(0xE6) |

| |

|

#define | CADIC _SFR_MEM16(0xE8) |

| |

|

#define | CADICL _SFR_MEM8(0xE8) |

| |

|

#define | CADICH _SFR_MEM8(0xE9) |

| |

|

#define | FCSR _SFR_MEM8(0xF0) |

| |

|

#define | DUVRD 3 |

| |

|

#define | CPS 2 |

| |

|

#define | DFE 1 |

| |

|

#define | CFE 0 |

| |

|

#define | BPIMSK _SFR_MEM8(0xF2) |

| |

|

#define | SCIE 4 |

| |

|

#define | DOCIE 3 |

| |

|

#define | COCIE 2 |

| |

|

#define | DHCIE 1 |

| |

|

#define | CHCIE 0 |

| |

|

#define | BPIFR _SFR_MEM8(0xF3) |

| |

|

#define | SCIF 4 |

| |

|

#define | DOCIF 3 |

| |

|

#define | COCIF 2 |

| |

|

#define | DHCIF 1 |

| |

|

#define | CHCIF 0 |

| |

|

#define | BPSCD _SFR_MEM8(0xF5) |

| |

|

#define | BPDOCD _SFR_MEM8(0xF6) |

| |

|

#define | BPCOCD _SFR_MEM8(0xF7) |

| |

|

#define | BPDHCD _SFR_MEM8(0xF8) |

| |

|

#define | BPCHCD _SFR_MEM8(0xF9) |

| |

|

#define | BPSCTR _SFR_MEM8(0xFA) |

| |

|

#define | BPOCTR _SFR_MEM8(0xFB) |

| |

|

#define | BPHCTR _SFR_MEM8(0xFC) |

| |

|

#define | BPCR _SFR_MEM8(0xFD) |

| |

|

#define | SCD 4 |

| |

|

#define | DOCD 3 |

| |

|

#define | COCD 2 |

| |

|

#define | DHCD 1 |

| |

|

#define | CHCD 0 |

| |

|

#define | BPPLR _SFR_MEM8(0xFE) |

| |

|

#define | BPPLE 1 |

| |

|

#define | BPPL 0 |

| |

|

#define | BPINT_vect _VECTOR(1) |

| |

|

#define | VREGMON_vect _VECTOR(2) |

| |

|

#define | INT0_vect _VECTOR(3) |

| |

|

#define | INT1_vect _VECTOR(4) |

| |

|

#define | INT2_vect _VECTOR(5) |

| |

|

#define | WDT_vect _VECTOR(6) |

| |

|

#define | TIMER1_IC_vect _VECTOR(7) |

| |

|

#define | TIMER1_COMPA_vect _VECTOR(8) |

| |

|

#define | TIMER1_COMPB_vect _VECTOR(9) |

| |

|

#define | TIMER1_OVF_vect _VECTOR(10) |

| |

|

#define | TIMER0_IC_vect _VECTOR(11) |

| |

|

#define | TIMER0_COMPA_vect _VECTOR(12) |

| |

|

#define | TIMER0_COMPB_vect _VECTOR(13) |

| |

|

#define | TIMER0_OVF_vect _VECTOR(14) |

| |

|

#define | SPI_STC_vect _VECTOR(15) |

| |

|

#define | VADC_vect _VECTOR(16) |

| |

|

#define | CCADC_CONV_vect _VECTOR(17) |

| |

|

#define | CCADC_REG_CUR_vect _VECTOR(18) |

| |

|

#define | CCADC_ACC_vect _VECTOR(19) |

| |

|

#define | EE_READY_vect _VECTOR(20) |

| |

|

#define | _VECTORS_SIZE 42 |

| |

Definitions for ATmega8HVA and ATmega16HVA.

This file should only be included from <avr/io.h>, never directly.

1.8.13

1.8.13