#include <sys/param.h>#include <sys/systm.h>#include <sys/mbuf.h>#include <netinet/in.h>#include <netinet/in_systm.h>#include <netinet/ip.h>#include <netinet/ip_var.h>

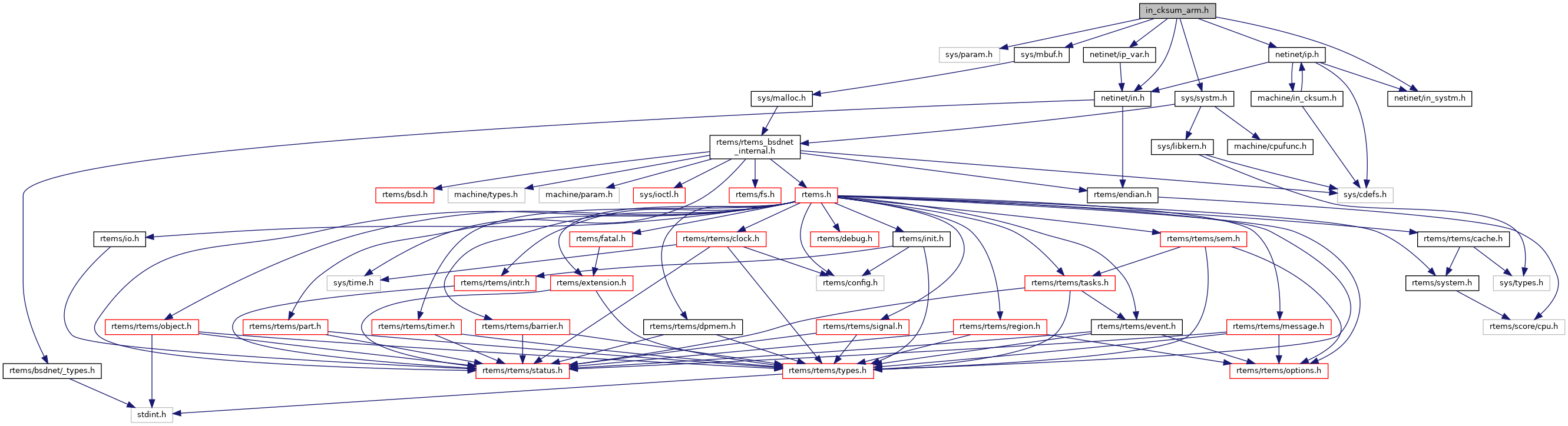

Include dependency graph for in_cksum_arm.h:

Go to the source code of this file.

Functions | |

| int | in_cksum (struct mbuf *m, int len) |

| int | in4_cksum (struct mbuf *m, u_int8_t nxt, int off, int len) |

Macro Definition Documentation

◆ ADD16

| #define ADD16 |

Value:

__asm __volatile(" \n\ ldmia %0!, {%2, %3, %4, %5} \n\ adds %1,%7,%2; adcs %1,%1,%3 \n\ adcs %1,%1,%4; adcs %1,%1,%5 \n\ adcs %1,%1,#0\n" \

: "=r" (w), "=r" (sum), "=&r" (tmp1), "=&r" (tmp2), "=&r" (tmp3), "=&r" (tmp4) \

: "0" (w), "r" (sum) \

: "cc")

◆ ADD32

| #define ADD32 |

Value:

__asm __volatile(" \n\ ldmia %0!, {%2, %3, %4, %5} \n\ adds %1,%7,%2; adcs %1,%1,%3 \n\ adcs %1,%1,%4; adcs %1,%1,%5 \n\ ldmia %0!, {%2, %3, %4, %5} \n\ adcs %1,%1,%2; adcs %1,%1,%3 \n\ adcs %1,%1,%4; adcs %1,%1,%5 \n\ adcs %1,%1,#0\n" \

: "=r" (w), "=r" (sum), "=&r" (tmp1), "=&r" (tmp2), "=&r" (tmp3), "=&r" (tmp4) \

: "0" (w), "r" (sum) \

: "cc")

◆ ADD4

| #define ADD4 |

Value:

__asm __volatile(" \n\ ldr %2,[%0],#4 \n\ adds %1,%4,%2 \n\ adcs %1,%1,#0\n" \

: "=r" (w), "=r" (sum), "=&r" (tmp1) \

: "0" (w), "r" (sum) \

: "cc")

◆ ADD64

| #define ADD64 |

Value:

__asm __volatile(" \n\ ldmia %0!, {%2, %3, %4, %5} \n\ adds %1,%7,%2; adcs %1,%1,%3 \n\ adcs %1,%1,%4; adcs %1,%1,%5 \n\ ldmia %0!, {%2, %3, %4, %5} \n\ adcs %1,%1,%2; adcs %1,%1,%3 \n\ adcs %1,%1,%4; adcs %1,%1,%5 \n\ ldmia %0!, {%2, %3, %4, %5} \n\ adcs %1,%1,%2; adcs %1,%1,%3 \n\ adcs %1,%1,%4; adcs %1,%1,%5 \n\ ldmia %0!, {%2, %3, %4, %5} \n\ adcs %1,%1,%2; adcs %1,%1,%3 \n\ adcs %1,%1,%4; adcs %1,%1,%5 \n\ adcs %1,%1,#0\n" \

: "=r" (w), "=r" (sum), "=&r" (tmp1), "=&r" (tmp2), "=&r" (tmp3), "=&r" (tmp4) \

: "0" (w), "r" (sum) \

: "cc")

◆ ADD8

| #define ADD8 |

Value:

__asm __volatile(" \n\ ldmia %0!, {%2, %3} \n\ adds %1,%5,%2; adcs %1,%1,%3 \n\ adcs %1,%1,#0\n" \

: "=r" (w), "=r" (sum), "=&r" (tmp1), "=&r" (tmp2) \

: "0" (w), "r" (sum) \

: "cc" )

◆ REDUCE

| #define REDUCE |

Value:

__asm __volatile(" \n\ mov %2, #0x00ff \n\ orr %2, %2, #0xff00 \n\ and %2, %0, %2 \n\ add %0, %2, %0, lsr #16\n" \

: "=r" (sum) \

: "0" (sum), "r" (tmp1))

1.8.13

1.8.13