Motorola M68K CPU Dependent Source. More...

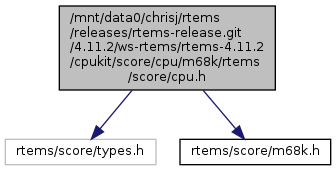

Include dependency graph for cpu.h:

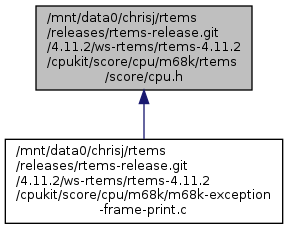

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Data Structures | |

| struct | Context_Control |

| This defines the minimal set of integer and processor state registers that must be saved during a voluntary context switch from one thread to another. More... | |

| struct | Context_Control_fp |

| This defines the complete set of floating point registers that must be saved during any context switch from one thread to another. More... | |

| struct | Context_Control_fp |

| This defines the complete set of floating point registers that must be saved during any context switch from one thread to another. More... | |

| struct | CPU_Interrupt_frame |

| This defines the set of integer and processor state registers that must be saved during an interrupt. More... | |

| struct | CPU_Exception_frame |

| The set of registers that specifies the complete processor state. More... | |

| struct | _CPU_ISR_handler_entry |

Macros | |

| #define | CPU_INLINE_ENABLE_DISPATCH TRUE |

| #define | CPU_SIMPLE_VECTORED_INTERRUPTS TRUE |

| #define | CPU_HAS_SOFTWARE_INTERRUPT_STACK 1 |

| #define | CPU_HAS_HARDWARE_INTERRUPT_STACK 0 |

| #define | CPU_ALLOCATE_INTERRUPT_STACK 1 |

| #define | CPU_ISR_PASSES_FRAME_POINTER 0 |

| #define | CPU_HARDWARE_FP FALSE |

| #define | CPU_SOFTWARE_FP FALSE |

| #define | CPU_ALL_TASKS_ARE_FP FALSE |

| #define | CPU_IDLE_TASK_IS_FP FALSE |

| #define | CPU_USE_DEFERRED_FP_SWITCH TRUE |

| #define | CPU_PROVIDES_IDLE_THREAD_BODY TRUE |

| #define | CPU_STACK_GROWS_UP FALSE |

| #define | CPU_STRUCTURE_ALIGNMENT __attribute__ ((aligned (4))) |

| #define | CPU_TIMESTAMP_USE_STRUCT_TIMESPEC TRUE |

| #define | CPU_BIG_ENDIAN TRUE |

| #define | CPU_LITTLE_ENDIAN FALSE |

| #define | CPU_PER_CPU_CONTROL_SIZE 0 |

| #define | M68K_FP_STATE_SIZE 216 |

| #define | _CPU_Context_Get_SP(_context) (_context)->a7_msp |

| #define | _CPU_Context_Fp_start(_base, _offset) ((void *) _Addresses_Add_offset( (_base), (_offset) ) ) |

| #define | _CPU_Context_Initialize_fp(_fp_area) |

| #define | _CPU_Context_Fp_start(_base, _offset) |

| #define | _CPU_Context_Initialize_fp(_fp_area) |

| #define | M68K_MOVE_A7 0x3F3C |

| #define | M68K_JMP 0x4EF9 |

| #define | CPU_MODES_INTERRUPT_LEVEL 0x00000007 /* interrupt level in mode */ |

| #define | CPU_MODES_INTERRUPT_MASK 0x00000007 /* interrupt level in mode */ |

| #define | CPU_CONTEXT_FP_SIZE sizeof( Context_Control_fp ) |

| #define | CPU_MPCI_RECEIVE_SERVER_EXTRA_STACK 1024 |

| #define | CPU_INTERRUPT_NUMBER_OF_VECTORS 256 |

| #define | CPU_INTERRUPT_MAXIMUM_VECTOR_NUMBER (CPU_INTERRUPT_NUMBER_OF_VECTORS - 1) |

| #define | CPU_PROVIDES_ISR_IS_IN_PROGRESS FALSE |

| #define | CPU_STACK_MINIMUM_SIZE M68K_CPU_STACK_MINIMUM_SIZE |

| #define | CPU_PRIORITY_MAXIMUM M68K_CPU_PRIORITY_MAXIMUM |

| #define | CPU_SIZEOF_POINTER 4 |

| #define | CPU_ALIGNMENT 4 |

| #define | CPU_HEAP_ALIGNMENT CPU_ALIGNMENT |

| #define | CPU_PARTITION_ALIGNMENT CPU_ALIGNMENT |

| #define | CPU_STACK_ALIGNMENT 0 |

| #define | _CPU_Initialize_vectors() |

| #define | _CPU_ISR_Disable(_level) m68k_disable_interrupts( _level ) |

| #define | _CPU_ISR_Enable(_level) m68k_enable_interrupts( _level ) |

| #define | _CPU_ISR_Flash(_level) m68k_flash_interrupts( _level ) |

| #define | _CPU_ISR_Set_level(_newlevel) m68k_set_interrupt_level( _newlevel ) |

| #define | _CPU_Fatal_halt(_source, _error) |

| #define | CPU_USE_GENERIC_BITFIELD_CODE FALSE |

| #define | CPU_USE_GENERIC_BITFIELD_DATA FALSE |

| #define | _CPU_Bitfield_Find_first_bit(_value, _output) |

| #define | _CPU_Priority_Mask(_bit_number) ( 0x8000 >> (_bit_number) ) |

| #define | _CPU_Priority_bits_index(_priority) (_priority) |

Typedefs | |

| typedef uint32_t | CPU_Counter_ticks |

Functions | |

| uint32_t | _CPU_ISR_Get_level (void) |

| Return the current interrupt disable level for this task in the format used by the interrupt level portion of the task mode. More... | |

| void | _CPU_Context_Initialize (Context_Control *the_context, void *stack_area_begin, size_t stack_area_size, uint32_t new_level, void(*entry_point)(void), bool is_fp, void *tls_area) |

| Initializes the CPU context. More... | |

| void * | _CPU_Thread_Idle_body (uintptr_t ignored) |

| This routine is the CPU dependent IDLE thread body. More... | |

| void | _CPU_Initialize (void) |

| CPU initialization. More... | |

| void | _CPU_ISR_install_raw_handler (uint32_t vector, proc_ptr new_handler, proc_ptr *old_handler) |

| This routine installs a "raw" interrupt handler directly into the processor's vector table. More... | |

| void | _CPU_ISR_install_vector (uint32_t vector, proc_ptr new_handler, proc_ptr *old_handler) |

| This routine installs an interrupt vector. More... | |

| void | _CPU_Install_interrupt_stack (void) |

| This routine installs the hardware interrupt stack pointer. More... | |

| void | _CPU_Context_switch (Context_Control *run, Context_Control *heir) |

| CPU switch context. More... | |

| void | _CPU_Context_Restart_self (Context_Control *the_context) |

| void | _CPU_Context_save_fp (Context_Control_fp **fp_context_ptr) |

| This routine saves the floating point context passed to it. More... | |

| void | _CPU_Context_restore_fp (Context_Control_fp **fp_context_ptr) |

| This routine restores the floating point context passed to it. More... | |

| void | _CPU_Exception_frame_print (const CPU_Exception_frame *frame) |

| This method prints the CPU exception frame. More... | |

| CPU_Counter_ticks | _CPU_Counter_read (void) |

Variables | |

| void * | _VBR |

| SCORE_EXTERN _CPU_ISR_handler_entry | _CPU_ISR_jump_table [256] |

| const unsigned char | _CPU_m68k_BFFFO_table [256] |

Detailed Description

Motorola M68K CPU Dependent Source.

This include file contains information pertaining to the Motorola m68xxx processor family.

Macro Definition Documentation

◆ _CPU_Bitfield_Find_first_bit

| #define _CPU_Bitfield_Find_first_bit | ( | _value, | |

| _output | |||

| ) |

Value:

{ \

register int dumby; \

\

__asm__ volatile ( " move.w %2,%1\n" \

" lsr.w #8,%1\n" \

" beq.s 1f\n" \

" move.b (%3,%1.w),%0\n" \

" and.l #0x000000ff,%0\n"\

" bra.s 0f\n" \

"1: moveq.l #8,%0\n" \

" add.b (%3,%2.w),%0\n" \

"0:\n" \

: "=&d" ((_output)), "=&d" ((dumby)) \

: "d" ((_value)), "ao" ((_CPU_m68k_BFFFO_table)) \

: "cc" ) ; \

}

◆ _CPU_Context_Fp_start

| #define _CPU_Context_Fp_start | ( | _base, | |

| _offset | |||

| ) |

Value:

( \

(void *) _Addresses_Add_offset( \

(_base), \

(_offset) + CPU_CONTEXT_FP_SIZE - 4 \

) \

)

RTEMS_INLINE_ROUTINE void * _Addresses_Add_offset(const void *base, uintptr_t offset)

Add offset to an address.

Definition: address.h:50

#define CPU_CONTEXT_FP_SIZE

The size of the floating point context area.

Definition: cpu.h:539

◆ _CPU_Context_Initialize_fp [1/2]

| #define _CPU_Context_Initialize_fp | ( | _fp_area | ) |

Value:

{ \

Context_Control_fp *_fp; \

_fp = *(Context_Control_fp **)_fp_area; \

_fp->_exception_bits = 0; \

_fp->_trap_enable_bits = 0; \

_fp->_sticky_bits = 0; \

_fp->_rounding_mode = 0; /* ROUND_TO_NEAREST */ \

_fp->_format = 0; /* NIL */ \

_fp->_last_operation = 0; /* NOOP */ \

_fp->_operand1.df = 0; \

_fp->_operand2.df = 0; \

}

This defines the complete set of floating point registers that must be saved during any context switc...

Definition: cpu.h:294

◆ _CPU_Context_Initialize_fp [2/2]

| #define _CPU_Context_Initialize_fp | ( | _fp_area | ) |

Value:

{ \

uint32_t *_fp_context = (uint32_t *)*(_fp_area); \

*(--(_fp_context)) = 0; \

*(_fp_area) = (void *)(_fp_context); \

}

◆ _CPU_Fatal_halt

| #define _CPU_Fatal_halt | ( | _source, | |

| _error | |||

| ) |

1.8.13

1.8.13